## W. Hennig XIA LLC, 2744 East 11th St, Oakland, CA www.xia.com

Supported by DOE grant DE-SC0017223

*Phase I: 2017-2018, Phase II: 2018 – 2020 (2022)*

## Contents

- Motivation

- DAQ development

- Timing Measurements

- Performance Tests

- Commercial Branches

- Summary

## Motivation

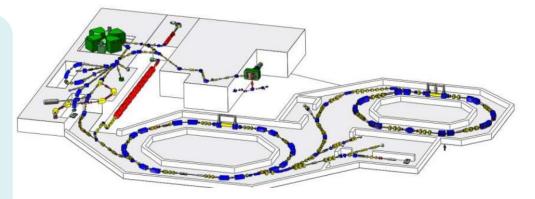

Large nuclear physics experiments often use physically separated radiation detectors

Electronics to read out detectors must be synchronized to 100ns-100ps, ideally <10ps

Traditionally use dedicated clock and trigger cables for synchronization ⊗

Modern technologies allow time synchronization through data network

New DAQ electronics with White Rabbit / PTP synchronization XIA has been developing digital data acquisition electronics for radiation detector applications for over 20 years

## Motivation

## **XIA SBIR Project Goals**

- Adapt IEEE 1588 Precision Time Protocol technologies to XIA's detector readout DAQ modules for clocking and develop a "software triggering" concept

- □ Stay within standards, use open HW/SW environment, remain compatible

- ⇒ Phase I: Standard PTP (1588-2008) and Synchronous Ethernet achieved tens of ns precision

- $\Rightarrow$  Phase II: White Rabbit (now 1588-2019 high accuracy profile) "WR"

- Requirements for timing precision depends on experiment

- Background reduction by coincidence:

- Event building for detector arrays:

- Time of flight measurements:

- Goal in SBIR topics:

- => "useable" if better than 1 ns

Hundreds of nanoseconds Tens of nanoseconds Sub-nanosecond "10 ns"; "1 ns or better"

### Detector Readout Electronics Synchronized Through Ethernet Network Timing Techniques

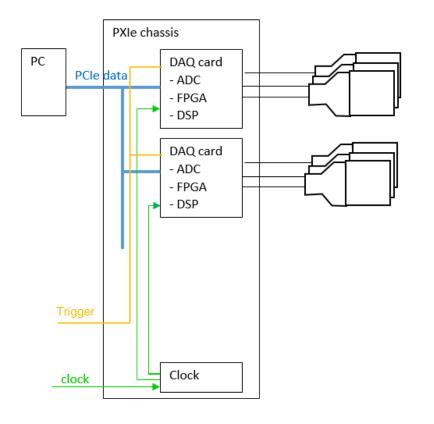

### Traditional

Crate with data I/O to host PC and backplane clock/trigger distribution

## Tag detector data with backplane clock (48bit)

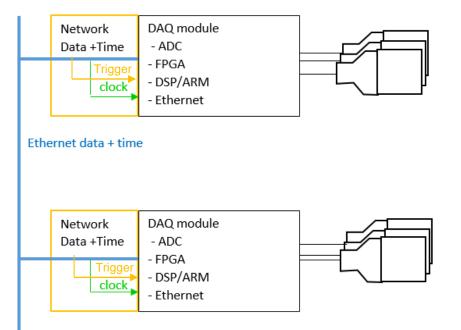

### This Project

Independent modules with network data, derived clock, and "software trigger"

Tag detector data with UTC-related timestamps (date/time to ns precision)

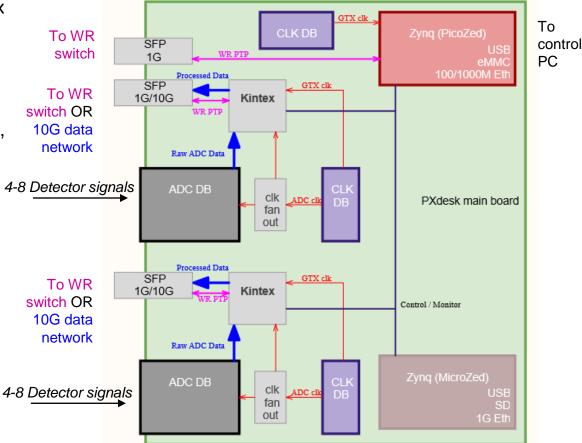

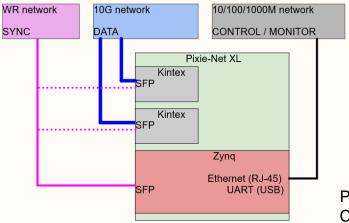

## Phase II DAQ hardware: Pixie-Net XL (PXdesk), Revision B

- Pulse processor board using Kintex 7 FPGA

- Zynq controller board (Linux) for control/monitor.

- ADC daughtercards for detector readout (flexibility in ADC channels, rate, precision, or non-ADC functions)

- High speed data flow from ADC to FPGA to Ethernet output

- Rev. B updates:

- WR clocking circuitry on DB

- WR option for Zynq

- Rogers PCB material for 10G

Goals for this module:

<100ps timing resolution 10G Ethernet ... ready for a 10G WR switch High rate pulse processing Thick border = separate PCB

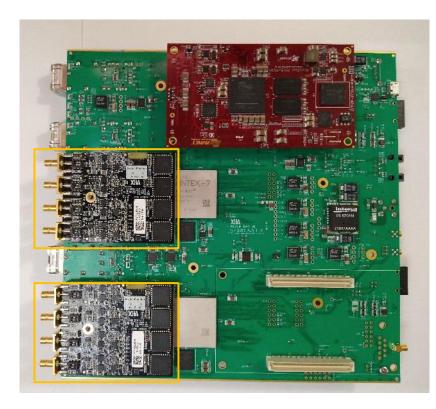

## Prototypes built so far

Main board with ADC daughtercards (black) and Zynq controller module (red).

### **Daughtercards**

#### DB01:

4-channel, 12-**14**bit, 75-**125** MSPS ADCs variable gain/offset, uses ¼ of the I/O pins

#### DB02:

8-channel, **12**-14bit, **250** MSPS ADCs fixed gain/offset, differential inputs

#### DB06:

4-channel, **16**bit, **250** MSPS or 14bit, 500 MSPS ADCs 2 gains, variable offset

#### DB04:

8-channel, 12-**14**bit, **250** MSPS ADCs fixed gain, variable offset, microcoax inputs

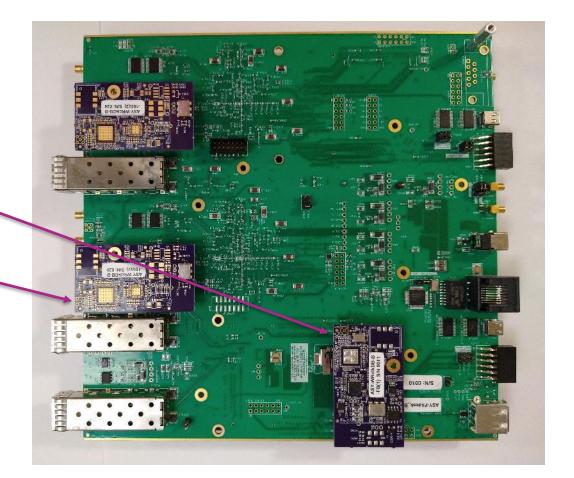

## **Clocking and Synchronization**

Rev B boards move WR clocking circuitry to a daughtercard to accommodate different modes of operation for ADC and Ethernet:

#### 1. WRclkDB (1G):

WR voltage controlled oscillators, DACs, PROMs 125 MHz for 1G Ethernet (and ADC) option for "low jitter DB" circuitry

#### 2. WRclkDB (10G)

Simple fixed oscillator, no WR sync 156.25 MHz for 10G Ethernet

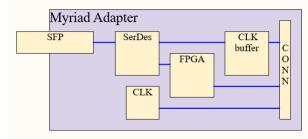

#### 3. Myriad Adapter:

SFP and SerDes TTCL to decode Myriad I/O Compatibility for DGS, Greta, etc "Myriad clock" for ADC Separate 156.25 MHz for 10G Ethernet (collaboration with ANL, in progress)

Main board with clock DBs for Kintex and Zynq

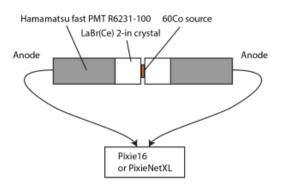

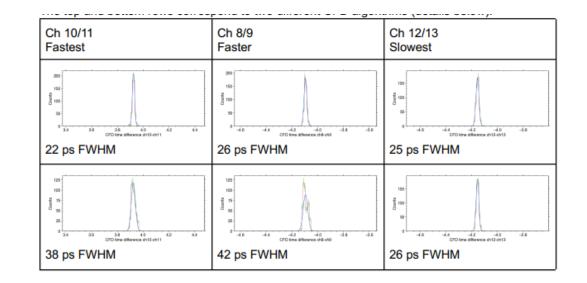

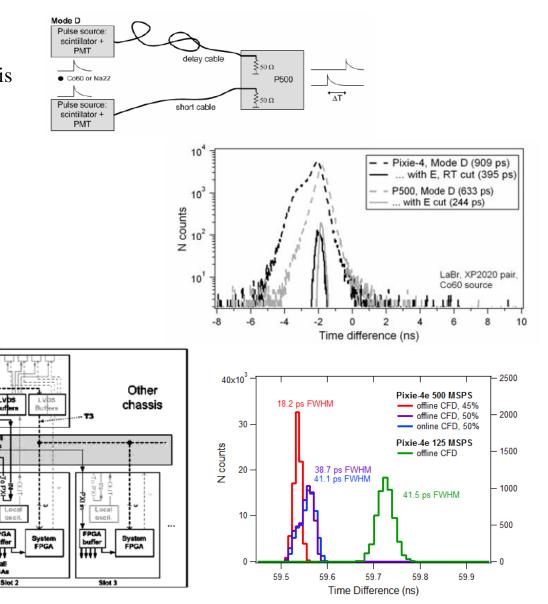

## Timing Measurements: Same-module CFD Timing (DB04, UTK)

### Split NIM signal using channel pairs with different input bandwidth

#### There is no significant difference in the resolution.

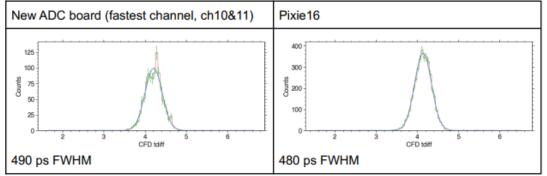

Real detector, comparison to Pixie-16

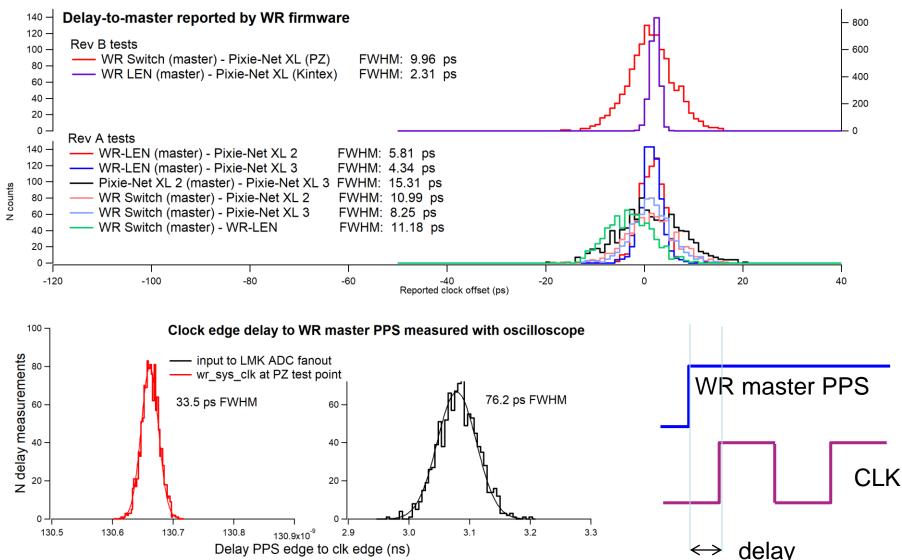

## **Timing Measurements: FW log and Oscilloscope**

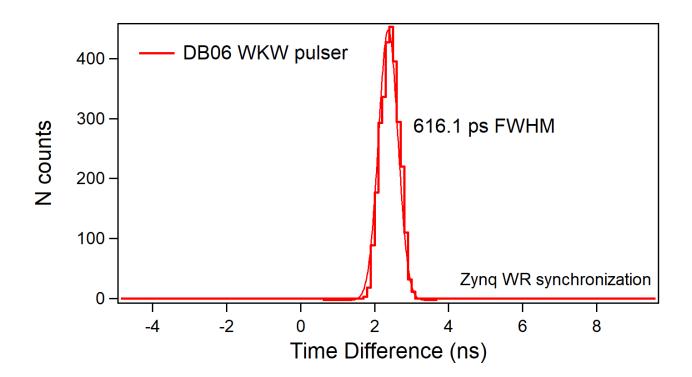

### Timing Measurements: 2-module CFD Timing DB06 (preliminary)

- > Not great for a split pulser, but ok for some slower detectors

- Need to improve clock distribution path from Zynq to ADCs

- Need to improve signal source and input bandwidth

- Need to tune CFD parameters

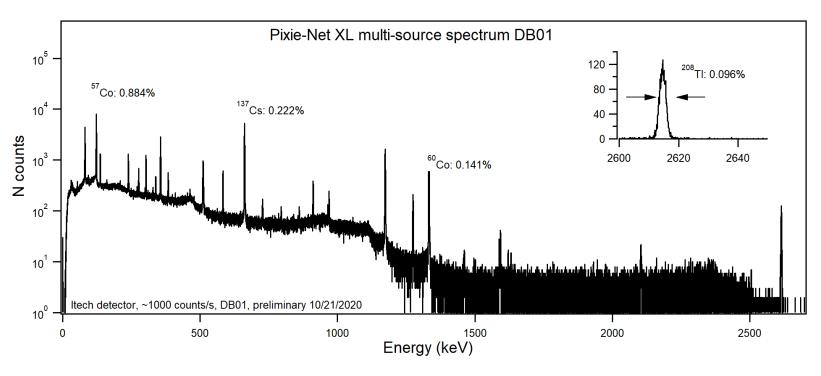

## **Energy Resolution**

**Pixie-Net XL HPGe energy resolution (DB01)**

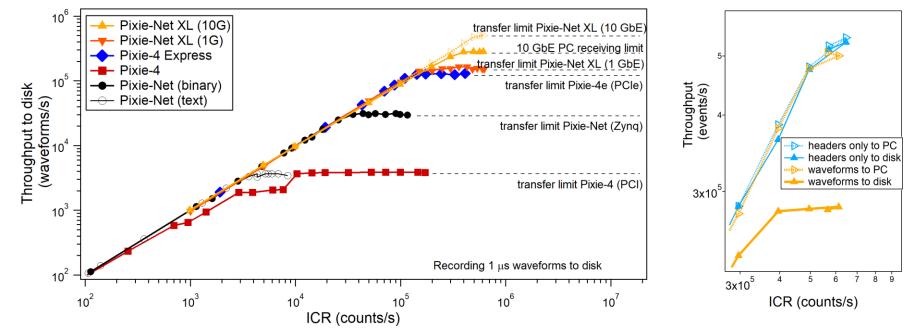

## List Mode Data Throughput

- Pixie-Net XL exceeds previous models' throughput for storing event waveforms to disk

- Limited by packets dropped by PC (not by network) try multiple PCs?

- Almost 300,000 waveforms/s (or over 500,000 headers/s) per Kintex

Preferred setup architecture uses 3 networks (SYNC, CONTROL, DATA) Could be all one network, but with lower throughput (two are max 1G)

## **Commercial Product**

#### **Pixie-Net XL**

Several units sold to beta testers 3<sup>rd</sup> party funds for custom features

#### Operation

Can use single or multiple PCs for ...

| 🛃 ISANASIA - ANDERSONA - ANDERSONA                                           | (www.VI               | ,                           |

|------------------------------------------------------------------------------|-----------------------|-----------------------------|

| File Celt Setup Control Window                                               |                       |                             |

| PlaideNetComon.c.backup                                                      | d3.w3.min.ja          | pashiatprojpage.html.backup |

|                                                                              |                       | prannetanojacje dibet       |

| FinisHettreman.h.heolog                                                      |                       |                             |

| FisieMet/Common.0                                                            | findsettings          | rspage.html                 |

|                                                                              |                       | Portabala                   |

|                                                                              |                       | stunetaetae . e             |

| Fisie Met/Losfigue                                                           |                       | excertation and             |

|                                                                              |                       | webbings and                |

|                                                                              |                       | wettinger i ni dankop       |

| Fimie Net Hanual.docx                                                        |                       | sizarad. c                  |

| Plate Net Namal.pdt                                                          |                       | startidag                   |

|                                                                              |                       | estan talon pas             |

| itilebenesettings.ini                                                        |                       | educe failing an            |

| Zia IZC web header.jpg                                                       |                       | weite 220                   |

|                                                                              |                       | weither Street              |

| energi tena theata / was/waa                                                 |                       |                             |

| team_amore[0] sill be                                                        | rounded off to = 1.20 | 10010 us, 320 samples       |

| TRACE lEMOTE[1] will be rounded off to - 0.250010 us, 64 samples             |                       |                             |

| TRACE TRACE()] will be enabled all by 7 1.220000 and 220 supplier            |                       |                             |

| <pre>reason_isome[2] will be rounded off to = 1.200000 ms, 220 samples</pre> |                       |                             |

| ADC board tesperature: 57 C                                                  |                       |                             |

| Zyng kesperature: 64 C                                                       |                       |                             |

| teriaion 2990, Serial M                                                      |                       |                             |

| cost@localhoat:/vas/wew                                                      | 4                     |                             |

|                                                                              | /                     | 1                           |

|                                                                              | v cch /r              | ar wohnada                  |

| LIIIU/                                                                       | <u>, 2211 ((</u>      | or webpage                  |

|                                                                              |                       |                             |

| -                                                                            |                       |                             |

| for setu                                                                     | ന നന്ദ്രം             |                             |

| OF SETU                                                                      | ก คมส เ               | 120                         |

|                                                                              |                       |                             |

| Pixie-Net ADC Traces (current)                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Correct ADC<br>Total<br>Correct ADC<br>Total<br>Correct ADC<br>Correct ADC<br>Correct ADC<br>Mode Sector<br>Web Interface | 9020<br>4030<br>20020<br>20020<br>2002<br>1000<br>0<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2002<br>2 |  |  |  |  |

|                                                                                                                           | Show AF Table AF<br>Show AF Table F songle T songle T songle<br>A songle FA songle T songle T songle T<br>a songle J songle F songle T songle T songle F<br>A songle J songle F songle F songle T songle T<br>A songle F songle F songle T songle T<br>A songle F songle F songle T songle T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

...webpages to monitor results and status

## Commercial Branches: SBIR work adopted in other XIA products\*

Pixie-Net PTP

Phase I PTP prototype commercially available. Several units sold

### • Pixie-16 MZ-TrigIO

Trigger I/O module for XIA's 6U PXI pulse processor boards with PTP clock option Several units sold Also available as desktop PTP GPIO module

### • Pixie-4 Hybrid

Update of XIA's 3U PXIe pulse processor board Optional WR synchronization and 1G data output Reusing same ADC daughtercards Product released October 2020

### • Pixie-16 x1/x2

Update of XIA's Pixie-16 pulse processor board "HW ready" for WR + 1G data Reusing same ADC daughtercards, up to 32 channels per board Product release Fall 2021

### Summary

- Implemented WR network time synchronization on new detector DAQ electronics, the Pixie-Net XL

- Easily reaches "<1 ns" timing resolution goal but needs more tweaks to reach "best WR" performance of <20ps (in progress)</li>

- List mode data output via 10G Ethernet max. measured output data rate is ~600 MB/s (test mode, one Kintex) max. LM data rate received is ~360 MB/s max (header only, one Kintex)

## Outlook

- Performance testing, more beta testing at NP labs, and product release

- Complete Myriad adapter

- ➤ Waiting for 10G WR switch …

Detector Readout Electronics Synchronized Through Ethernet Network Timing Techniques

## Thank You

## **Questions?**

## **Existing Technologies**

### \* Shared Clock Signal

Works, but requires dedicated cabling. Not ideal for distributed DAQ systems. Reported time resolution: sub-nanosecond, even tens of picoseconds

### ✤ IEEE 1588 Precision Time Protocol (PTP)

Processors exchange synchronization messages over network to measure delays PTP Time Stamping Units (TSU) built into several commercial Ethernet MACs, Ethernet physical layers (PHY). Commercial PTP switches available (\$\$). Open source software for managing time synchronization (LinuxPTP, ptpd) Reported time resolutions: milliseconds (software TSU) low nanoseconds (hardware TSU)

#### Synchronous Ethernet (SyncE)

Extract clock from Ethernet link and use for local processing

### ✤ CERN's White Rabbit (WR)

Extension of PTP standard with synchronous Ethernet Open hardware project. WR network switch commercially available. WR modules developed by scientists

Reported time resolution:

sub-nanosecond, even tens of picoseconds

### **Detector Readout Electronics Synchronized Through Ethernet Network Timing Techniques**

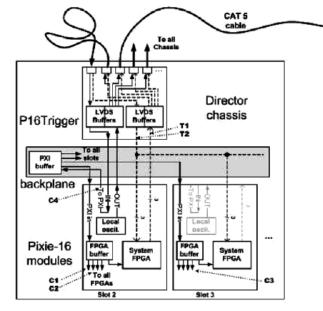

P16Trigger

backplane

Pixie-16

modules

C6

Ŗ

FPGA

buffer

**,,,**,

To all

FPGAs

## **Traditional Synchronization**

Traditionally, time synchronization between multiple channels of digital data acquisition is accomplished by sharing clocks, clock reset signals, and triggers.

With suitable algorithms (CFD), timing resolutions can be  $\sim 20$  ps for idealized signals and a few hundred ps for detector signals digitized with 100-5000 MSPS.

## **UDP Data Output Discussion**

### Pro:

- □ Simple to implement in FPGA (WR code) and on receiving side

- Easy transfer to one or more storage nodes

- □ Faster

### Contra:

| Possible loss of data | but 1 packet = 1 event          |

|-----------------------|---------------------------------|

|                       | but how bad is it actually? [*] |

- Possible data out of sequence but all packets timestamped

- □ Error checking needs to be pushed to "higher level application"

- => Will look into firmware updates for UDP package management or for TCP

\* (M.J. Christensen et al: Achieving reliable UDP transmission at 10 Gb/s using BSD socket for data acquisition systems, arXiv:1706.00333v1 [physics.ins-det] 1 Jun 2017)

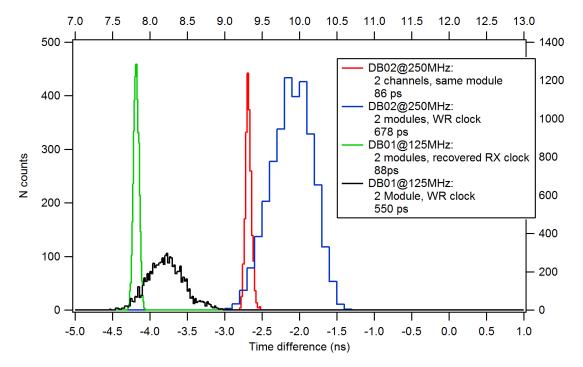

### Timing Measurements – Rev. A with pulser

### **Time Resolutions**

- $\Rightarrow$  With 75 MHz ADC daughtercard, pulser, tuned WR clock:

- ⇒ With 250 MHz ADC daughtercard, pulser, tuned WR clock: (2 channels in same module: 86 ps FWHM)

550 ps FWHM 678 ps FWHM

$\Rightarrow$  With 125MHz ADC daughtercard, pulser, recovered RX clock: 88 ps FWHM