## W. Hennig, S. Hoover XIA LLC, 31057 Genstar Rd, Hayward, CA www.xia.com

Supported by DOE grant DE-SC0017223

*Phase I: 2017-2018, Phase II: 2018 – 2020 (2021)*

## Contents

- Motivation

- DAQ HW and FW development

- Timing Measurements

- Software Triggering

- Preliminary Performance Tests

- Commercial Branches

- Summary

## Motivation

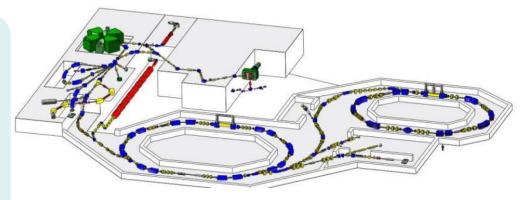

Large nuclear physics experiments often use physically separated radiation detectors

Electronics to read out detectors must be synchronized to 100ns-100ps, ideally <10ps

Traditionally use clock/trigger cables for synchronization ☺

Modern technologies allow time synchronization through data network

New DAQ electronics with White Rabbit / PTP synchronization XIA has been developing digital data acquisition electronics for radiation detector applications for over 20 years

## Motivation

## **XIA SBIR Project Goals**

- Adapt IEEE 1588 Precision Time Protocol technologies to XIA's detector readout DAQ modules for clocking and develop a "software triggering" concept

- □ Stay within standards, use open HW/SW environment, remain compatible

- ⇒ Phase I: Standard PTP (1588-2008) and Synchronous Ethernet

- $\Rightarrow$  Phase II: White Rabbit (now 1588-2019 high accuracy profile)

- Requirements for timing precision depends on experiment

- Background reduction by coincidence:

- Event building for detector arrays:

- Time of flight measurements:

- Goal in SBIR topics:

Hundreds of nanoseconds Tens of nanoseconds Sub-nanosecond "10 ns"; "1 ns or better"

#### Detector Readout Electronics Synchronized Through Ethernet Network Timing Techniques

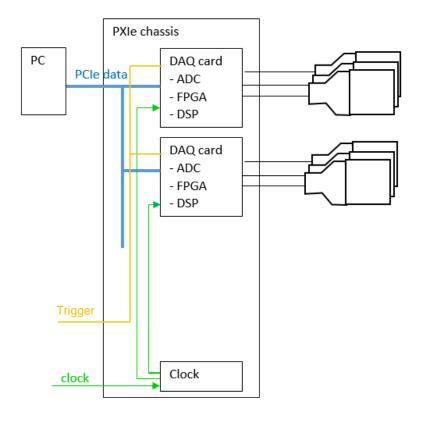

#### Traditional

Crate with data I/O to host PC and backplane clock/trigger distribution

## Tag detector data with backplane clock (48bit)

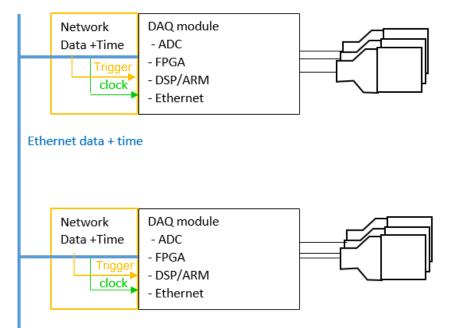

#### This Project

Independent modules with network data, derived clock, and "software trigger"

Tag detector data with UTC-related timestamps (date/time to ns precision)

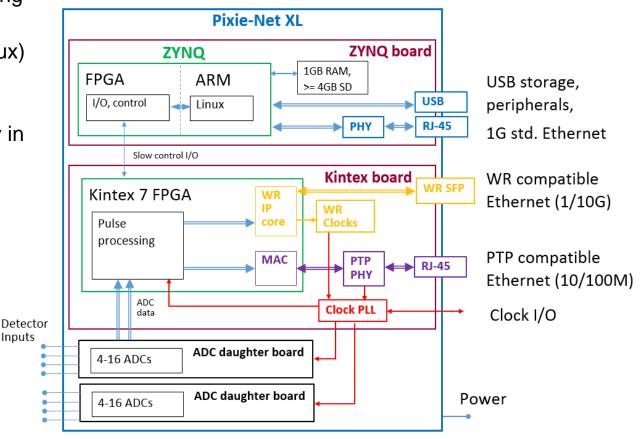

## Phase II DAQ hardware: Pixie-Net XL (PXdesk)

- Pulse processor board using Kintex 7 FPGA

- Zynq controller board (Linux) for setup, diagnostics.

- ADC daughtercards for detector readout (flexibility in ADC channels, rate, precision, or non-ADC functions)

- High speed data flow from ADC to FPGA to Ethernet output

- WR, PTP, SyncE can be used as source for ADC and FPGA clocking

Goals:

<100ps timing resolution 10G Ethernet high rate pulse processing

### Prototypes built so far

Main board with ADC daughtercards and Zynq controller module card stack

4-channel, 75-125 MHz, 14bit ADC daughtercard

4-channel, 16bit, 250 MHz or 14bit, 500 MHz ADC daughtercard

8-channel, 250 MHz, 12bit ADC daughtercard Differential inputs via HDMI cable

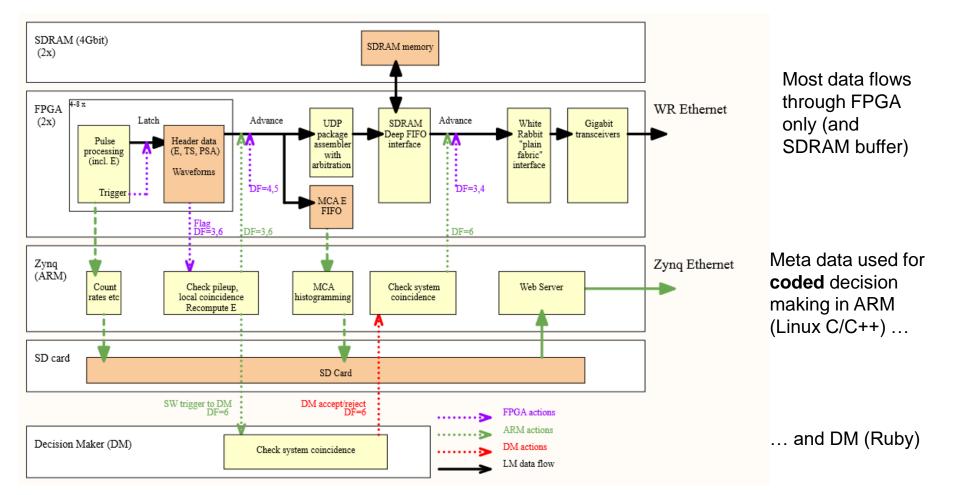

### **Firmware implementation**

Integrated WR open source IP core into XIA pulse processing

- => Pixie-Net XL can

- capture detector pulse data and compute energy, MCA histograms, CFD timing, etc

- tune local clocks for WR and ADC to WR master (frequency + phase)

- record WR date/time in captured detector data

- send out Ethernet data via WR core

#### Top level module Controller I/O XIA Pulse processing WR board logic (CLBv2 wrapper) TS for ADC input pulses xwrc\_platform (Xilinx K7) GTX Trigger logic CUTE DAC controller Pulse proc. WR/ADC Data for Reset logic clocking Eth. out xwrc\_board\_common wr core pinout xdc

XIA pulse processing adapted to Kintex board WR open source unchanged WR open source adapted

#### FW block diagram

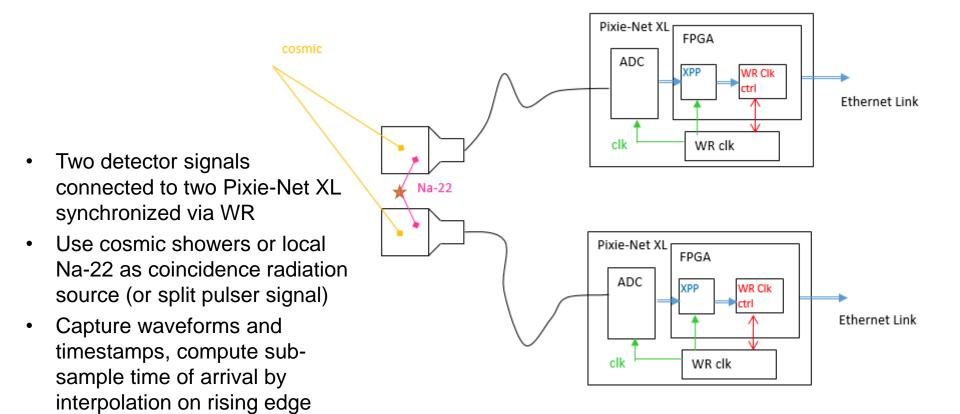

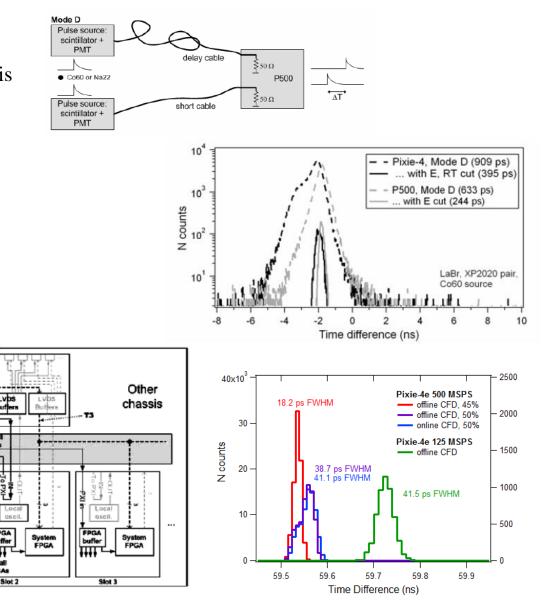

### **Timing Measurements To Characterize Synchronization**

(CFD)

apply Gauss fit

Histogram the difference of

time of arrival in both modules,

### **Timing Measurements – Pulser**

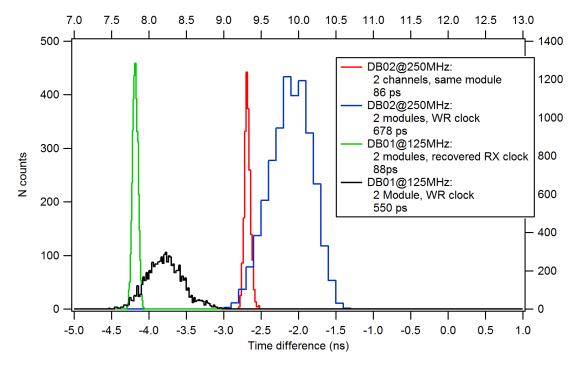

#### **Time Resolutions**

- $\Rightarrow$  With 75 MHz ADC daughtercard, pulser, tuned WR clock:

- $\Rightarrow$  With 250 MHz ADC daughtercard, pulser, tuned WR clock: (2 channels in same module: 86 ps FWHM)

550 ps FWHM 678 ps FWHM

$\Rightarrow$  With 125MHz ADC daughtercard, pulser, recovered RX clock: 88 ps FWHM

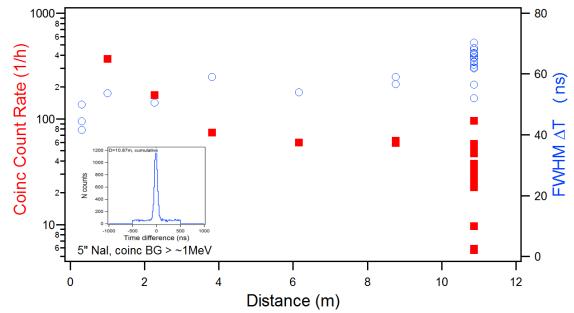

### **Timing Measurements – Cosmic coincidences**

- Demonstrating synchronization over long time and large distance (goal is not high precision)

- Only use WR time stamps, not waveform interpolation

- $\Rightarrow$  Background rate ~500 counts/s each detector, recording ~8.5 million records (>1 MeV) per day.

- $\Rightarrow$  Coincidence rate decreases with distance. Hundreds of coincidence events per day at ~11m distance.

- $\Rightarrow$  Timing resolution ~70 ns FWHM

If modules could share trigger information besides clock synchronization, we would not have to record the 99.984% waste data => use Software Triggering

(P. Auger, et al ", Rev. Mod. Phys. 11, 288 (1939). https://doi.org/10.1103/RevModPhys.11.288 )

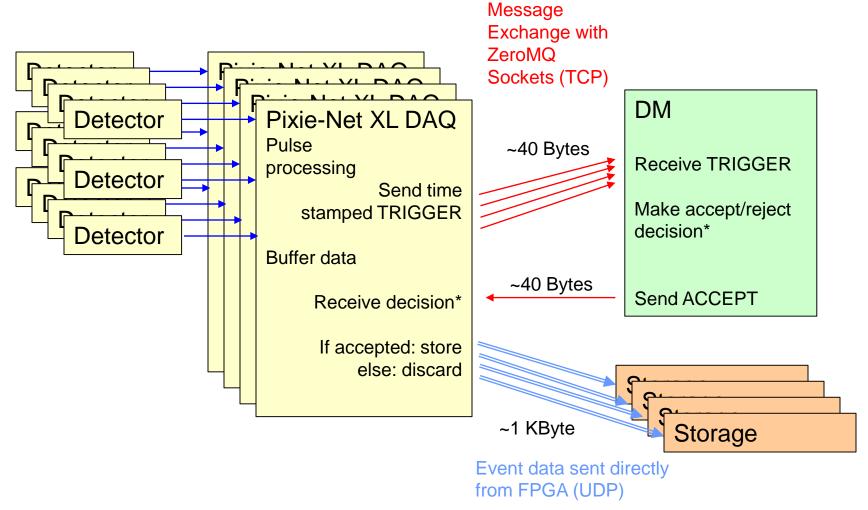

### **Software Triggering: Overview**

\* = coded decision making, based on WR time stamp, hit pattern, history, ...

### **Software Triggering: Implementation**

Various "Data Flow" options, can also simply output all data from FPGA and sort out offline

(xillybus.com/tutorials/deep-virtual-fifo-download-source)

## Software Triggering: Applied to Cosmic Coincidences

#### "Accept all local" mode:

- DM is programmed to respond with ACCEPT to all TRIGGER messages

- ARMs are programmed to approve records <u>matching time and channel</u> of the ACCEPT message i.e. **all local** triggers are approved;

- ACCEPT messages due to TRIGGERs from other DAQs are ignored)

- => Measured acceptance rates are 150-300 counts/s in 2 neighboring detectors.

#### "Coincidence only" mode:

- DM is programmed to respond ACCEPT to <u>all</u> TRIGGER messages

- ARMs approve records matching time but not channel of the ACCEPT message.

- i.e **local** events are approved **if** an event occurred within the coincidence window in the **other** DAQ. ACCEPT messages due to TRIGGERs from **local** DAQs are ignored.)

- => Measured acceptance rates are ~ 1-2% of the singles rate.

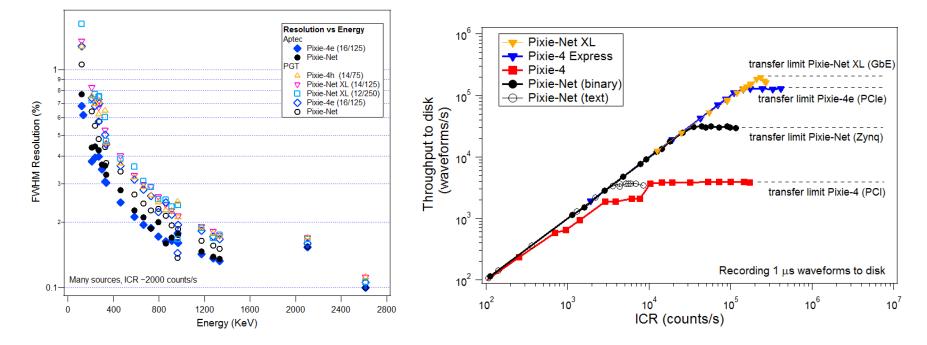

## **Other Performance Testing (preliminary)**

Pixie-Net XL HPGe energy resolution: matching older readout electronics.

Pixie-Net XL list mode throughput surpassing older electronics.

## Commercial Branches: SBIR work adopted in other XIA products\*

Pixie-Net PTP

Phase I PTP prototype commercially

available. Several units sold

#### Pixie-16 MZ-TrigIO

Trigger I/O module for XIA's 6U PXI pulse processor boards with PTP clock option. Several units sold. Also available as desktop PTP GPIO module

Pixie-4 Hybrid

Update of XIA's 3U PXIe pulse processor board with WR synchronization and data output. Reusing same ADC daughtercards Product release October 2020 (firm PO)

#### PXlarge

Update of XIA's Pixie-16 pulse processor board Reusing same ADC daughtercards. Product release est. March 2021

#### \* Mainly funded by XIA

### Summary

#### Hardware platform

- Implemented WR network time synchronization on new detector DAQ electronics, the Pixie-Net XL

- Easily reaches "<1 ns" timing resolution goal, demonstrated <100ps, but needs more tweaks to reach "best WR" performance of <20ps (in progress)</li>

### Software triggering

- Developed concept and demonstrated principle of operation

- Alternatives under consideration (Dolosse, White Rabbit Trigger Distribution)

## Outlook

- Upgrade Ethernet data to 10 Gbps rates (new WR switch under development)

- Performance testing, beta testing at NP labs, and product release (2021)

Detector Readout Electronics Synchronized Through Ethernet Network Timing Techniques

## Thank You

## **Questions?**

#### **Detector Readout Electronics Synchronized Through Ethernet Network Timing Techniques**

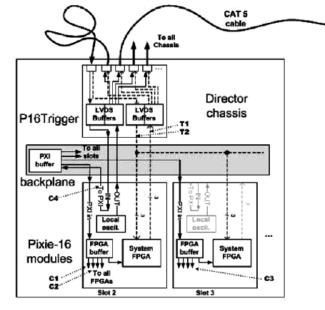

P16Trigger

backplane

Pixie-16

modules

C6

Ŗ

FPGA

buffer

**,,,**,

To all

FPGAs

### **Traditional Synchronization**

Traditionally, time synchronization between multiple channels of digital data acquisition is accomplished by sharing clocks, clock reset signals, and triggers.

With suitable algorithms (CFD), timing resolutions can be  $\sim 20$  ps for idealized signals and a few hundred ps for detector signals digitized with 100-5000 MSPS.

## **Existing Technologies**

#### \* Shared Clock Signal

Works, but requires dedicated cabling. Not ideal for distributed DAQ systems. Reported time resolution: sub-nanosecond, even tens of picoseconds

#### ✤ IEEE 1588 Precision Time Protocol (PTP)

Processors exchange synchronization messages over network to measure delays PTP Time Stamping Units (TSU) built into several commercial Ethernet MACs, Ethernet physical layers (PHY). Commercial PTP switches available (\$\$). Open source software for managing time synchronization (LinuxPTP, ptpd) Reported time resolutions: milliseconds (software TSU) low nanoseconds (hardware TSU)

#### Synchronous Ethernet (SyncE)

Extract clock from Ethernet link and use for local processing

#### ✤ CERN's White Rabbit (WR)

Extension of PTP standard with synchronous Ethernet Open hardware project. WR network switch commercially available. WR modules developed by scientists

Reported time resolution:

sub-nanosecond, even tens of picoseconds

### **UDP Data Output Discussion**

#### Pro:

- □ Simple to implement in FPGA (WR code) and on receiving side

- Easy transfer to one or more storage nodes

- □ Faster

#### Contra:

| Possible loss of data         | but 1 packet = 1 event            |

|-------------------------------|-----------------------------------|

|                               | but how bad is it actually? [Ref] |

|                               | but DM has TRIGGER data           |

| Possible data out of sequence | but all packets timestamped       |

□ Error checking pushed to "higher level application"

=> Will look into firmware updates for UDP package management or for TCP

(M.J. Christensen et al: Achieveing reliable UDP transmission at 10 Gb/s using BSD socket for data acquisition systems, arXiv:1706.00333v1 [physics.ins-det] 1 Jun 2017)