# **Multi-Channel Readout ASIC for Nuclear Physics Experiments**

**Presented by : Phaneendra Bikkina (Principal Engineer)**

#### DOE-NP SBIR/STTR Exchange Meeting August 14, 2019

Alphacore Inc. | www.alphacoreinc.com | Copyright ©2019 | PROPRIETARY | SBIR Data Rights

- Alphacore Overview

- Alphacore's DOE STTR Phase II Program Overview and Status (Year 1)

- Alphacore's Other Digitizers for Nuclear Physics Experiments

- Alphacore's Other Electronics Solutions for Nuclear Physics Experiments

- Other Relevant IP

- Summary

# **About Alphacore**

- Founded in 2012 and located in Arizona's "Silicon Desert"

- Providing technology that enable major advances in:

- Homeland Security

- Defense

- Aerospace

- Scientific Research

- Medical Imaging

- Product areas span:

- High performance analog, mixed signal, and RF electronics (radhard & conventional)

- High-speed visible light and infrared camera systems

- Robust GaN-based power electronics for space and high-energy physics experiments

- Innovative devices ensuring supply chain and IoT cybersecurity

Top 5

2017

#### Alphacore's Team

Alphacore's team is a combination of business and engineering professionals with long histories of delivering products and services to customers who demand state-of-the-art performance.

Our 70-person team has led successful careers at companies ranging from start-ups to multinationals including **Raytheon, Texas Instruments, Analog Devices, IDT, Bell Labs, Intel, United Technologies,** and **Honeywell**. Our Team includes 8 PhD-level full time employees and we sponsor 10 PhD students

# Multi-Channel Readout IC for Nuclear Physics Experiments

#### Multi-Channel Readout IC for Nuclear Physics Experiments: DOE STTR Phase II Year 1 Overview

- Program duration : 24 months

- Key goal of this work is to develop versatile and low-cost detector readout IC solutions.

- Two step approach that will lead to two fabrication runs

- In step 1 (tapeout 1), our approach is to produce three different types of chips in low cost 180nm process:

- multi-channel preamplifier/shaper IC (charge sensitive amplifiers )

- multi-channel ADC IC

- multi-channel combined IC that has preamplifiers, shaping amplifiers and ADCs with Serializers

- In step 2 (tapeout 2), our approach is to optimize the performance based on measurement results of tapeout 1 and add additional features to the ASICs:

- zero suppression logic

- increased resolution/performance of the ADCs

- optimized programmable charge sensitive amplifiers

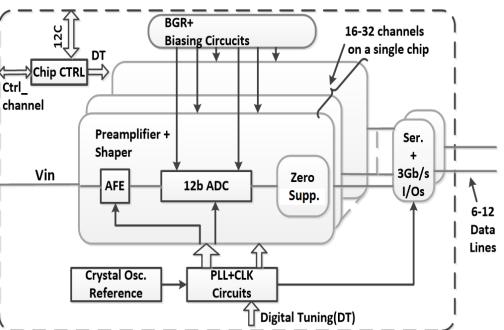

Top level architecture of Alphacore's proposed multi-channel ROIC chip that has Preamplifiers and Shapers, 12b/100MSPS ADCs, zero suppression logic, serializers and 1.6Gb/s I/Os. Zero suppression will reduce the data throughput very effectively in experiments where input pulse rate is low.

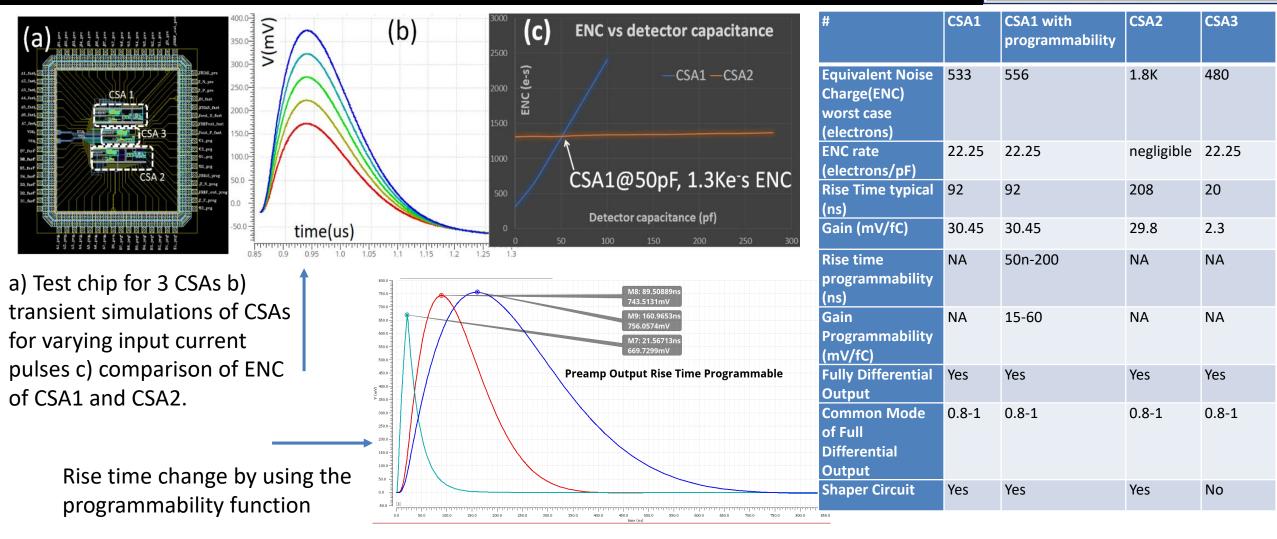

#### **Charge Sensitive Amplifiers**

8/19/2019

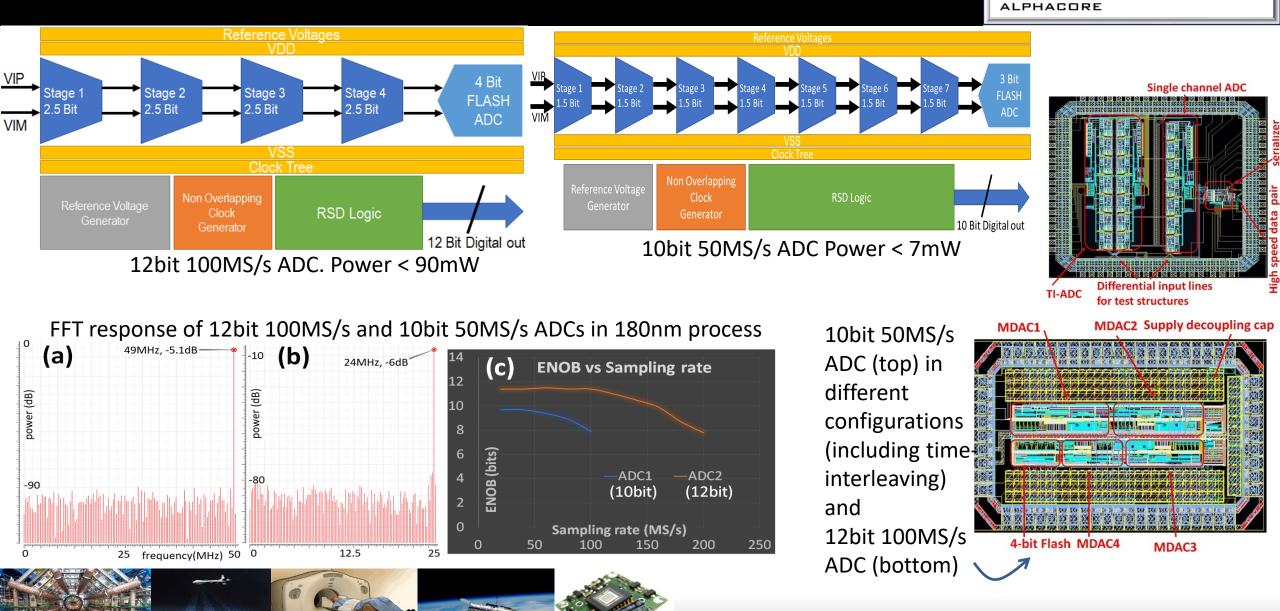

#### **Analog to Digital Converters**

Alphacore Inc. | www.alphacoreinc.com | Copyright ©2019 PROPRIETARY | SBIR Data Rights 8/19/2019

8

**Robust High**

Performance Microelectronics

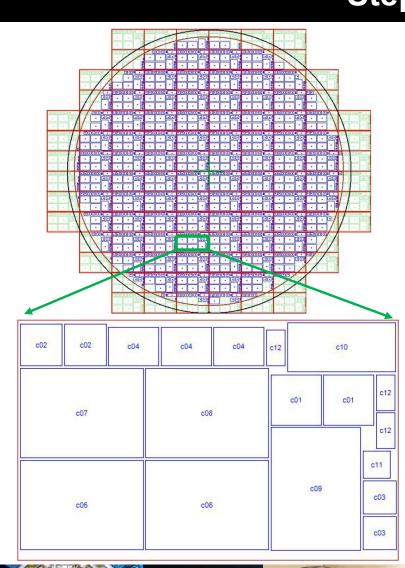

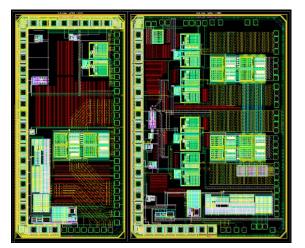

#### Multi-Channel Readout IC for Nuclear Physics Experiments: Step 1, Tapeout 1

| Chip<br>Name | Chip Part<br>Number | Design                                                         |  |

|--------------|---------------------|----------------------------------------------------------------|--|

| ADC          |                     | Standalone 12 bit ADC                                          |  |

|              |                     | Preamps Top_Level_preamp_test Top_Level_preamp_fast_test       |  |

|              | XF18002K18_7030     | Top_Level_preamp_programmable_test                             |  |

| CHIP1        | _01                 | Top_Level_preamp_cc_test Top_Level_preamp_cc_programmable_test |  |

|              | XF18002K18_7030     |                                                                |  |

| CHIP2        | _02                 | TI ADC+single channel TestADC +Serializer                      |  |

|              | XF18002K18_7030     |                                                                |  |

| CHIP3        | _03                 | 16to1 Serializer test structure                                |  |

|              | XF18002K18_7030     |                                                                |  |

| CHIP4        | _04                 | 3 different versions of pre-amps+10 BITADC                     |  |

|              | XF18002K18_7030     |                                                                |  |

| CHIP5        | _05                 | Multi Channel Preamp_Fast (16)                                 |  |

|              | XF18002K18_7030     |                                                                |  |

| CHIP6        | _06                 | Multi Channel Preamp_Programmable                              |  |

|              | XF18002K18_7030     |                                                                |  |

| CHIP7        | _07                 | Multi Channel Preamp_programmable_cc                           |  |

|              | XF18002K18_7030     |                                                                |  |

| CHIP8        | _08                 | Multi Channel 10-Bit ADC+Serializer                            |  |

|              | XF18002K18_7030     |                                                                |  |

| CHIP9        | _09                 | Multi 12BIT ADC+Serializer                                     |  |

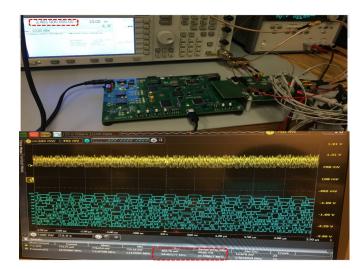

### **Current Status**

- All test chips fabricated.

- Critical test chips boards assembled. These include:

- 10bit 50MS/s ADC test chip

- 12bit 100MS/s ADC test chip

- CSA test chip test Serializer test chip

DeserializerSerializer

Testing started last week. Under progress. **Expected to** complete by end of September.

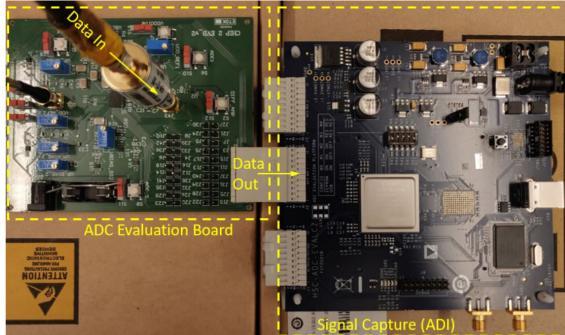

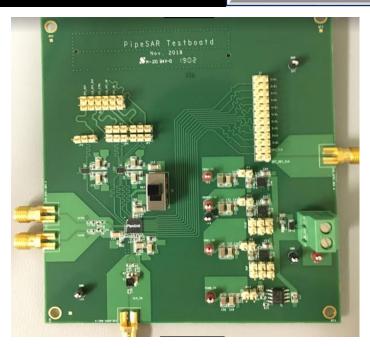

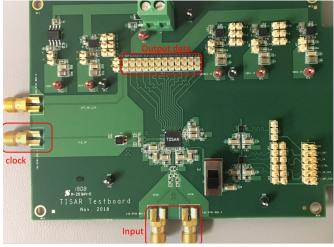

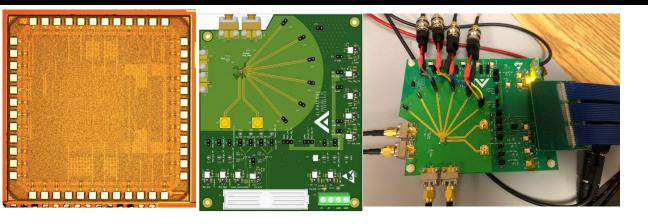

# ADC evaluation board with data capture and processing board

# Alphacore's Other Silicon Evaluated Digitizers for Nuclear Physics Experiments

Alphacore Inc. | www.alphacoreinc.com | Copyright ©20188/19/2019PROPRIETARY | SBIR Data Rights

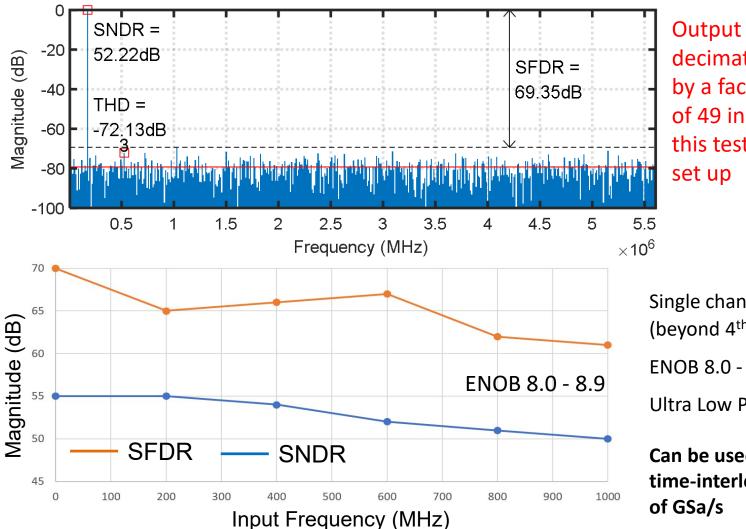

## A 10B500M, 10bit, 500MSa/s, Ultra Low Power ADC

Single channel ADC with wide input bandwidth (beyond 4<sup>th</sup> Nyquist zone)

ENOB 8.0 - 8.9 over four Nyquist bands

Ultra Low Power <1.18 mW (FOM <6.0fJ/conv.)

Can be used as the unit channel in a 10-bit, time-interleaved ADC with sample rate of tens of GSa/s

### Power dissipation breakdown

12

Alphacore Inc. | www.alphacoreinc.com | Copyright©2019 PROPRIETARY | SBIR Data Rights

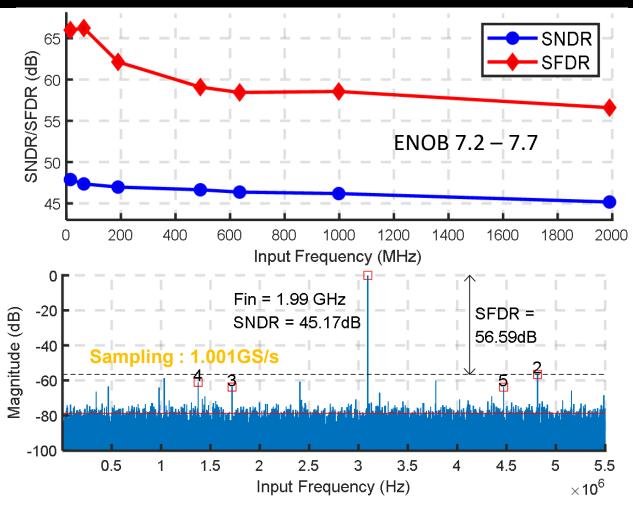

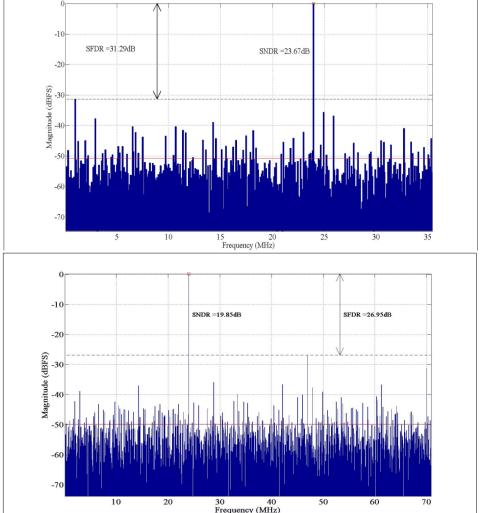

### A9B1G, Wide Input BW, 9-bit, 1GSa/s ADC

#### Output decimated by a factor of 91 in this testing set up

Single channel with **wide input bandwidth** (beyond 4<sup>th</sup> Nyquist zone)

ENOB stays within 7.2-7.7 over the first four Nyquist bands

Power <2.1mW (FOM < 10fJ/conv)

Can be used as the unit channel in a 10-bit, time-interleaved ADC with sample rate of tens of GSa/s

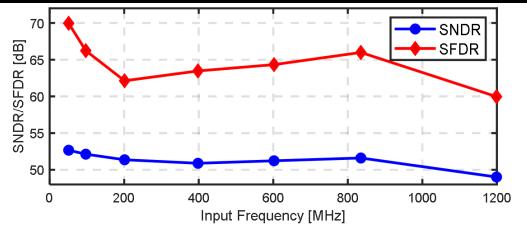

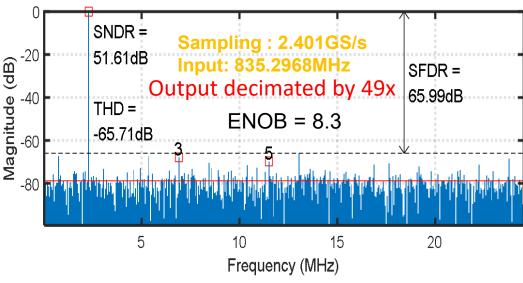

## A10B2G, 10 bit, 2.4GSa/s, Ultra Low Power ADC

The ADC has a **8-way** interleaved architecture, with combined sampling rate of 2.4GSa/s. The sampling rate is limited by on-chip clock buffers. Optimized buffers would deliver **up to 3.2GS/s with 6mW of additional power.**

We can interleave **16-way**(on-chip) to achieve **6.4GS/s for continuous digitization with no dead time**

The **developed calibration algorithm** has been shown to be very effective for the calibration of interleaving spurs, in this case yielding SFDR of 60-70 dB and ENOB that varies from 7.9 bits to 8.5 bits in the first Nyquist band.

Power < 6 mW (FOM < 6.9fJ/conv)

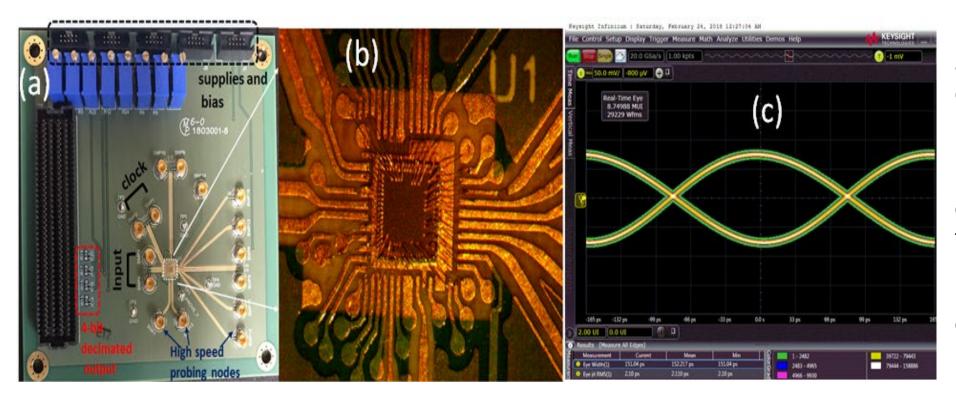

#### 20GS/s 20GHz 6bit ADC

**Robust High** Performance Microelectronics ALPHACORE

ENOB is 3.7 when tested at 9GSa/s and 8GHz input bandwidth

- IP functionality testing completed with a COB package.

- Development of a high-speed custom package with the lowest possible parasitics has been planned. The expected performance with a proper package is >4.5 ENOB, >20GSa/s, >20GHz and <300mW.

- The COB package and our current test setup allows testing the ADC at 16GSa/s and 8GHz.

- The goal is to be able to test beyond 20GSa/s sample rate and 20GHz input bandwidth

Measurements achieved for sampling frequencies up to 17.2GS/s with ENOB up to 3.3 bits

#### Output decimated by a factor of 126 in this testing setup

Alphacore Inc. | www.alphacoreinc.com | Copyright ©2019 PROPRIETARY | SBIR Data Rights

#### High Speed Interface (CML drivers)

a) Alphacore's high speed digitizer evaluation board with high speed CML drivers (data rate up to 12GB/s) b) micrograph of the die c) oscilloscope measurement of the CML drivers at 6GB/s (limited by our low data rate board design) with RMS jitter of 2ps.

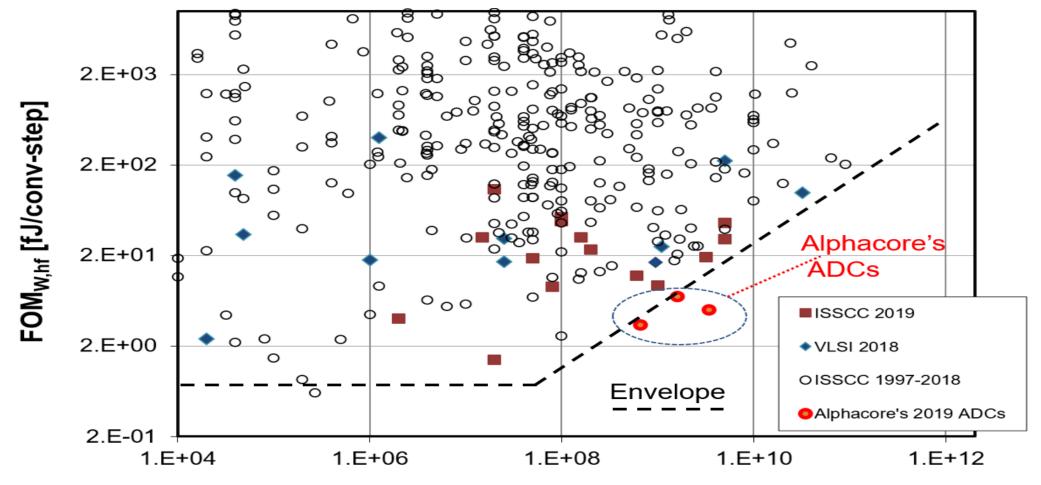

#### Alphacore's Ultra Low Power ADCs Walden Chart comparison: FOM vs Speed

f<sub>snyq</sub> [Hz]

8/19/2019

# Alphacore's Other Solutions for Nuclear Physics Experiments

Alphacore Inc. | www.alphacoreinc.com | Copyright ©2018 8/19/2019 PROPRIETARY | SBIR Data Rights

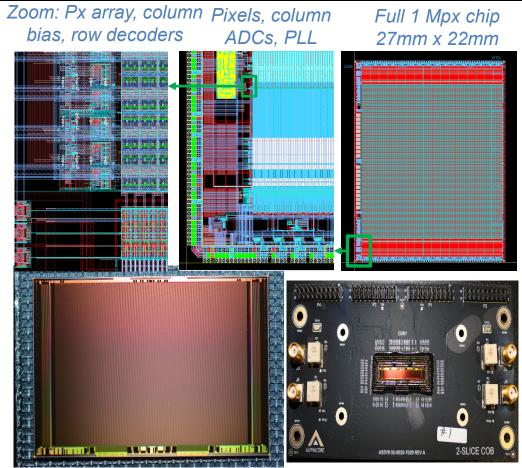

#### Radiation Hard High Speed Camera System for Accelerator Beam Diagnostics

1024 x 768 10,000 fps image sensor has been designed, fabricated, packaged and is currently under test.

10,000-pixel image sensor and camera has been designed, built and evaluated. It operates up to 20,000 fps

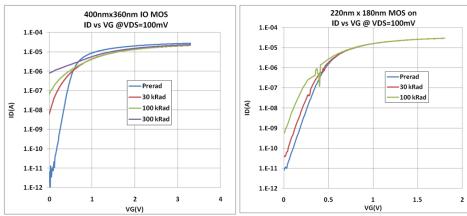

> Based on Co-60 tests, thick oxide NMOS has 100x higher leakage than core NMOS. The Alphacore image sensor uses core transistors for all supporting circuits outside the pixel array.

#### TID Effects in CMOS Transistors and Pixels

8/19/2019

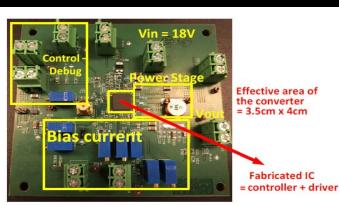

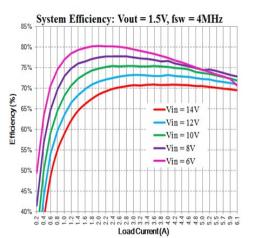

#### Radiation Hard Point of Load (POL) DC-DC Converter for Large Detector Systems

Large Detector Experiment

Alphacore's rad-hard POL converter controller ASIC

Alphacore's rad-hard POL converter evaluation board

Alphacore's rad-hard POL converter test results

POL DC-DC converter specs: 18V in, 1.2V – 5V out, 10A load current Efficiency > 70% Rad-hard to TID = 150Mrad High magnetic field tolerance (no ferrite core inductors used)

Large detector experiments can significantly benefit from high input voltage POL converters which enable bringing the power to the core chips in the form of "high voltage - low current". Cooling needs will be much lower.

These DC-DC Pol converters need to be very radhard and magnetic field tolerant. Alphacore has designed and demonstrated such a device in a DOE SBIR program. Dense medical imaging scanners is another application.

Alphacore Inc. | www.alphacoreinc.com | Copyright ©2019 PROPRIETARY | SBIR Data Rights

#### **Other Relevant IP**

|    | IP type                                                                  | Status                                        |

|----|--------------------------------------------------------------------------|-----------------------------------------------|

| 1  | 10b, 500MSPS, 2GHz, 1.2mW ADC core (radiation tolerant, 100krad)         | Evaluated                                     |

| 2  | 9b, 1GSPS, 2GHz, 2.7mW ADC core (radiation tolerant, 100krad)            | Evaluated                                     |

| 3  | 10b, 3GSPS, 3GHz, 18mW ADC core (radiation tolerant, 100krad)            | Evaluated                                     |

| 4  | 6b, 20GSPS, 20GHz, 220mW ADC core (radiation tolerant, 100krad)          | Evaluated                                     |

| 5  | Rad-hard multi-channel, 10-bit, 50MSPS, 7mW ADC ASIC (300krad)           | Under evaluation                              |

| 6  | Rad-hard multi-channel 12bit 100MS/s, 90mW ADC ASIC (300krad)            | Under evaluation                              |

|    | Rad-hard multi-channel 50-200 ns rise time, 1GHz CSA ASIC with (300krad) | Under evaluation                              |

| 6  | Rad-hard, 12-bit, 50MSPS, 9mW ADC (300krad)                              | Under evaluation                              |

| 7  | 6b, 5GSPS, 16GHz, 25mW ADC core (radiation tolerant, 100krad)            | Taped out                                     |

| 8  | 10b, 5GSPS, 36mW, 3GHz ADC core (radiation tolerant, 100krad)            | Tapeout Oct 2019                              |

| 9  | 8b, 100GSPS, 40GHz, 80mW ADC core                                        | Under design                                  |

| 10 | 12b, 500MSPS DAC (radiation tolerant, 100krad)                           | Evaluated                                     |

| 11 | 6GHz – 13GHz tunable, 360fs jitter PLL (radiation tolerant, 100krad)     | Evaluated                                     |

| 12 | 12Gb/s transceiver I/Os (radiation tolerant, 100krad)                    | Evaluated                                     |

| 13 | Rad-hard 56Gb/s PAM4 Transceiver (1Mrad)                                 | Tapeout in 2020                               |

| 14 | Rad-hard 27b dynamic range 256 X 256 IR DROIC (300krad)                  | Tapeout Sep 2019                              |

| 15 | Rad-hard 20b dynamic range 32 X 32 flash LIDAR receiver (300krad)        | Tapeout ready as of June 2019                 |

| 16 | Rad-hard 1Mpix, 10,000fps videocamera, 300krad                           | Under evaluation                              |

| 17 | Rad-hard DC-DC converter, 14V-to-1.5V, 7A, 1Mrad                         | Prototype tested (product chip under testing) |

| 18 | Rad-hard Li-Ion Battery monitor, 300krad                                 | Tapeout completed in June 2019                |

| 19 | In-package chip use time monitor                                         | Under evaluation                              |

| 20 |                                                                          | Evaluated (First prototype demoed)            |

| 21 | Rad-hard reconfigurable satellite power distribution ASIC, 300krad       | Tapeout August 2019                           |

| 22 |                                                                          | Tapeout Fall 2019                             |

| 23 |                                                                          | Tapeout Fall 2019                             |

| 24 | Sensor self-calibration monitor/controller                               | Taped out July 2019                           |

|    |                                                                          |                                               |

Alphacore Inc. | www.alphacoreinc.com | Copyright ©2019 PROPRIETARY | SBIR Data Rights

- The DOE Nuclear Physics STTR Phase II program reviewed in this presentation strengthens Alphacore's digitizer and readout ASIC family offered to Nuclear Physics, Scientific, Space and Defense customers.

- The program is advancing at a fast phase: Complete ASICs are currently being evaluated at the end of the Year 1.

- This presentation also summarized Alphacore's silicon evaluated ADCs and other IP relevant to Nuclear Physics researchers

Acknowledgement

Work on this program was funded by Department of Energy / Nuclear Physics, Grant #DE-SC00017074.

We especially appreciate the guidance by Dr. Manouchehr Farkhondeh and Dr. Michelle Shinn.

# Questions?