### How to reduce costs and power usage in front-end electronics by implementing a system-on-chip approach for data acquisition.

Isar Mostafanezhad, Ph.D.

Founder and CEO, Nalu Scientific, LLC

Aug 7, 2018

DOE Phase II SBIR Exchange Meeting

DE-SC0015231 Funded by DOE Office of NP

# About Nalu Scientific

#### **Mission statement:**

Design house for DOE electronics needs with commercial grade support

#### **Personnel:**

6 engineers and experimental physicists

40+ years combined experience

### Tools:

Commercial grade ASIC and electronic design tools

#### Funding:

DOE SBIRs and contracts

| ASIC Design                                     |

|-------------------------------------------------|

| Mixed signal System-on-Chip                     |

| Power optimization                              |

| Full suite commercial grade Cadence license and |

| server + design kits                            |

| Hardware Design                                 |

| FPGA, VHDL development                          |

| Implementation                                  |

| Bring up and debugging                          |

| Complex multi-layer boards                      |

| Expertise in:                                   |

| Fast time of flight measurements                |

| Readout electronics for HEP/NP                  |

## Mano Innovation Center

2800 Woodlawn Dr. Ste #240 Honolulu, HI 96822 <u>info@naluscientific.com</u> +1 (888) 717-6484

Waveform Digitizer SoCs for Single Photon Time of Fight Detection: Compact, Low Cost, Low Power

### **1. Various Chips:**

- Event based digitizer+DSP ٠

- 4-32 channel scope on chip •

- 1-10 Gsa/s, 12 bit res. .

- Low SWaP

- Low cost

- User friendly

- **2. Integration:** Detectors: •

- PMT

- SiPM

### Main application: Particle collider experiments

- 3. Other applications:

- Low light detection

- Picosecond timing

NALU SCIENTIFIC, LLC

SBIR Data Rights.

### Design and Fabrication of the ASoC: A System-on-Chip Data Acquisition System

### **Problem:**

We need new developments in instrumentation electronics with significantly improved energy, position, timing resolution, sensitivity, rate capability, stability, dynamic range, durability, pulse-shape discrimination capability, and background suppression.

### **Proposed Solution:**

Analog to digital converter System-on-Chip (ASoC)

### **Benefits:**

- High integration

- Analog and digital processing on a single chip

- High resolution waveforms at low cost and low power

- Feature extraction and background suppression in the front-end

2017 IEEE NSS-MIC, N-05 — Analog and Digital Circuit I

Nalu Scientific, LLC

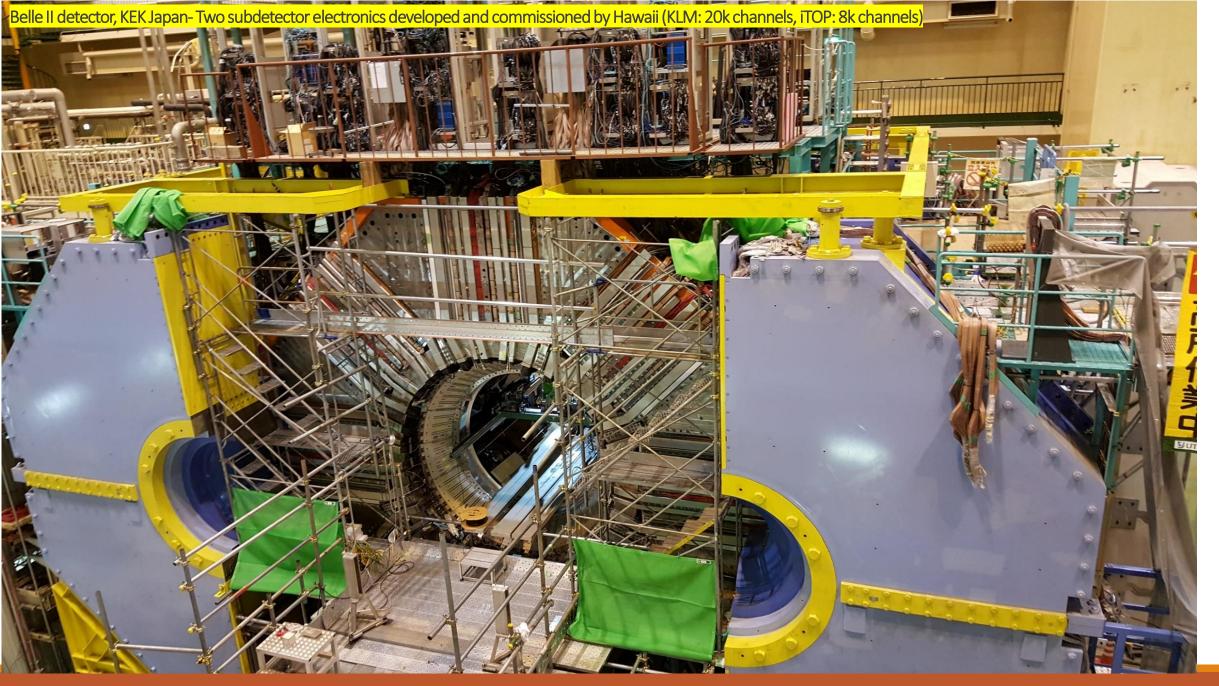

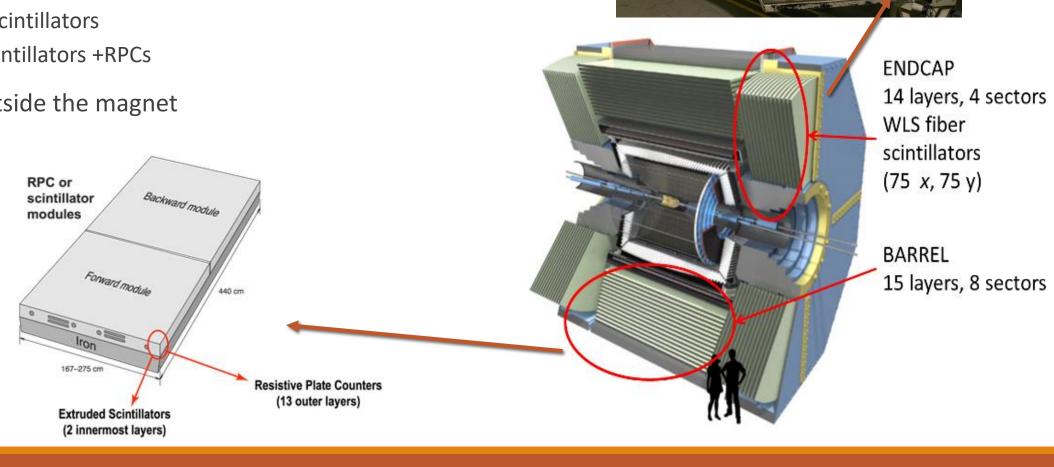

### Belle II: KLM Scintillator Upgrade 20k+ channels at 1 GSa/s ea.

KLM detectors:

Belle II

- Endcap: scintillators

- Barrel: scintillators +RPCs

Located outside the magnet

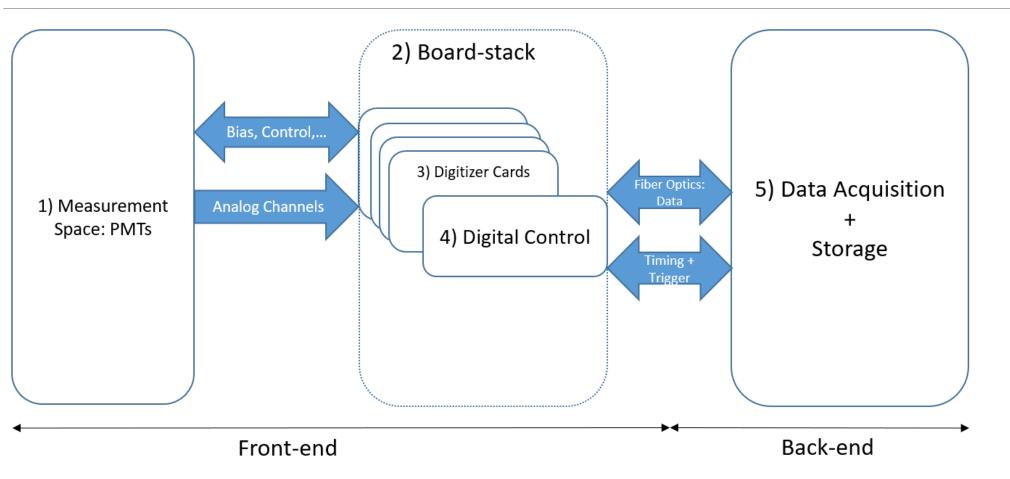

# Lesson learned 1: Classical HEP/NP Experiment

# Lessons learned 2: Opportunities

- Rad hard

- High performance

- Low cost

- Low power

- Highly integrated

- User friendly

Optimize to get to sweet spot = 2-3x gain

Solution: new design/SoC integration = <u>10 x gain</u>

Nalu Scientific Data Acquisition Systems

# Benefits of Higher Integration - SoC

### •Analog memory:

- Sampling always on (1-10 Gsa/s), but at low power

- Digitize only Region of Interest (ROI)

- Long analog buffer -> suitable for large experiments

### • Digital processing:

- Per channel cost reduction by a factor of 4

- Relax thermal design by 40% reduction in power dissipation

- Trigger time-stamping at the front-end

- Eliminating the need for costly high-end FPGAs

- User friendly: substantially reducing the FPGA firmware development labor

- Reduced complexity and design and cabling effort/cost for the front-end boards

# SBIR Project: ASoC- System on Chip

Compact, high performance waveform sampling- Funded Phase II

|         |     |      | - |  |

|---------|-----|------|---|--|

|         | -   | <br> |   |  |

| tronubu |     |      |   |  |

|         | - 5 |      | - |  |

|         |     |      |   |  |

|         | Г   |      |   |  |

|         | -   | <br> |   |  |

|         |     |      |   |  |

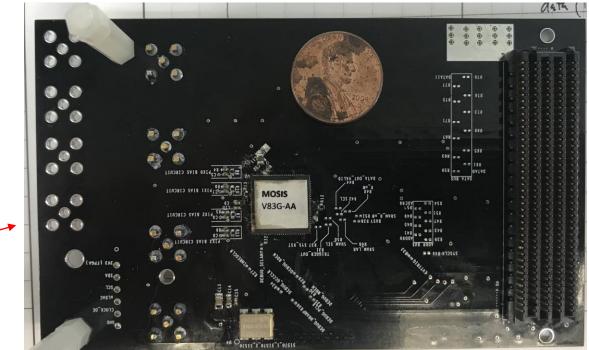

Fabricated ASoC Rev 1 die.

| Spec          |            |

|---------------|------------|

| Sampling rate | 2-4 Gsa/s  |

| ABW           | 0.9-1.5GHz |

| Depth         | 32k Sa     |

| N channels:   | 8-32       |

| Fab           | 250nm CMOS |

### **Key Contribution:**

- High performance digitizer: 3+ Gsa/s

- Highly integrated

- Commercially available

- 5mm x 5mm die size

### Funded DOE Phase II Project

All chips, are designed with commercial grade tools and licenses and can be sold once commercialized.

#### Nalu Scientific- ASIC developments

NALU SCIENTIFIC, LLC-

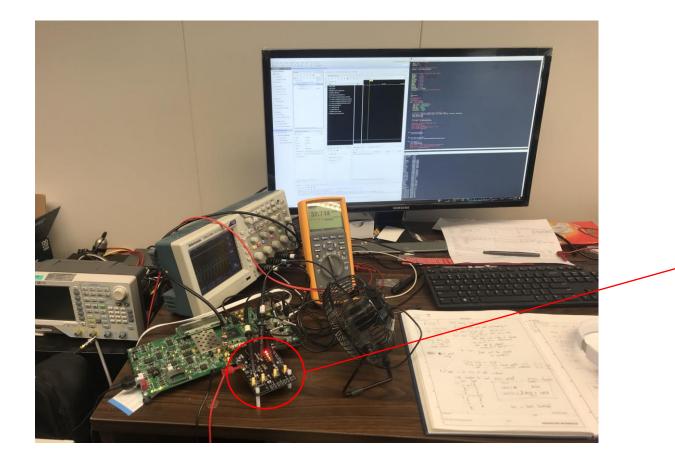

### ASoC Under test!

Results to be published at conferences and journals in the next 2-3 months.

### ASoC Evaluation FMC Card

# Current SoC-ASIC Projects

| Project  | Sampling<br>Frequency<br>(GHz) | Input BW<br>(GHz) | Buffer Length<br>(Samples) | Number of<br>Channels | Timing<br>Resolution (ps) | Integration | Built-in  | Readout     | Available<br>Date |

|----------|--------------------------------|-------------------|----------------------------|-----------------------|---------------------------|-------------|-----------|-------------|-------------------|

| ASoC     | 3-5                            | 0.8               | 32k                        | 4-8                   | 35                        | SoC         | Pre amps  | Parallel    | Aug 2018          |

| Siread   | 1-3                            | 0.7               | 4k                         | 64                    | 80-120                    | SoC         | Amp, bias | Fast serial | May 2018          |

| AARDVARC | 6-10                           | 2.5               | 32k                        | 4-8                   | 4-8                       | SoC         | Pre amps  | Fast serial | Sep 2018          |

- ASoC: Analog to digital converter System-on-Chip

- Rev 1 under test Eval card available

- **SiREAD**: SiPM specialized readout chip with bias and control

- Rev 1 under test

- **AARDVARC**: Variable rate readout chip for fast timing and low deadtime

- Rev 1 under test Phase II

All chips, are designed with commercial grade tools and licenses and can be sold once commercialized.

## Acknowledgements

- •DOE Office of Science

- •DOE SBIR/STTR Program

- •DOE Office of NP

- •From the team at Nalu Scientific: Thank you!