Novel Insulators in Silicon-on-Insulator Substrates to Improve Nuclear Physics Sensors and Circuits

July 29, 2025

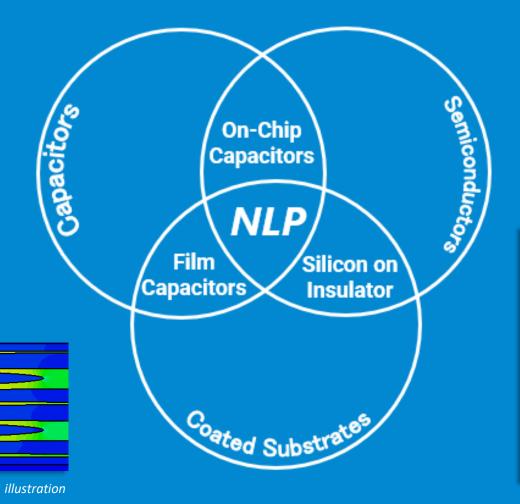

# Intro to Caporus & NLP™

# Silicon on Insulator for NP

Phase II Demonstration

# Caporus NLPTM

## Nanoscale Lamellar Porosity™ (NLP™)

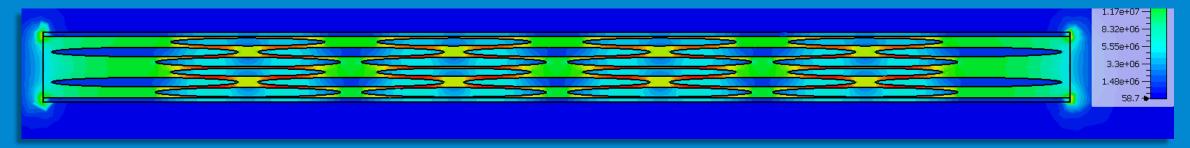

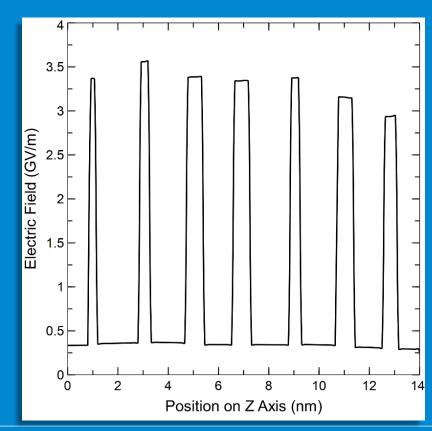

Controls the electric field distribution within a porous ceramic or semiconductor structure

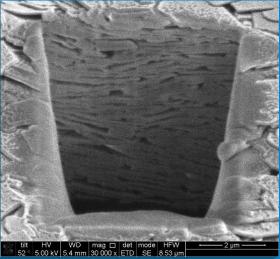

FIB image of material

Ceramic matrix (blue)

Porous regions (green)

Caporus Technologies, Inc.

# NLP™ Technology | Production at Scale

**Large Scale Slurry Production**

High-Volume Roll-to-Roll Manufacturing

Nanoscale Lamellar Porosity over Large Areas

Slurry-based coating for R2R deposition of ceramic coating - No sintering required

# NLP™ | Technology Overview

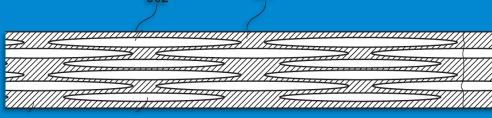

### **Caporus' Proprietary Nanoscale Lamellar Porosity**

- Structured porosity for electric field engineering

- Layered structure → redistribution of electric fields

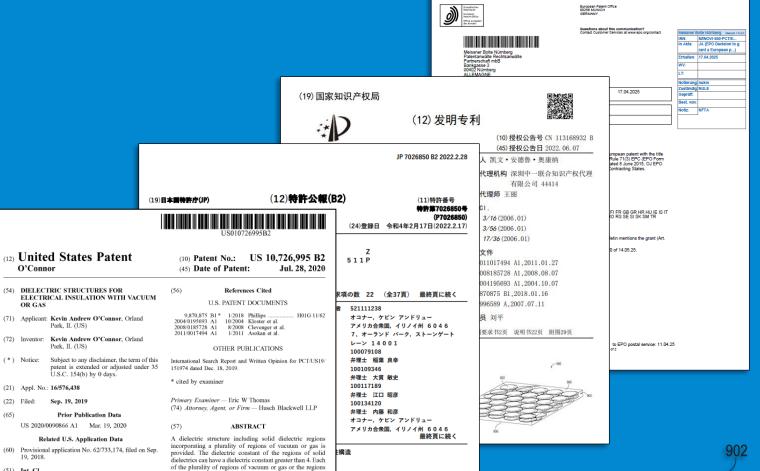

### Caporus | Issued IP

材料の1つ又は複数の領域であって

域のうちの少なくとも1つの領域は

子寸法 (d<sub>min</sub>) を有する、1つ

of solid dielectrics may be anisotropic with an aspect ratio

of at least four. The smallest average dimension of a plurality

of regions of vacuum or gas and/or solid dielectrics can have

a length of less than 1 micron. The dielectric structure may

have a higher electrical energy density in the regions of

vacuum or gas than in the solid matrix. One or more

electrodes of the capacitive structure can be coated with a

solid insulating layer without an interface between a region

22 Claims, 29 Drawing Sheets

of vacuum or gas and electrode.

**USPTO** issued July 2020 JPO issued March 2022 **CNIPA** issued June 2022 **EPO** issued May 2025

Note: additional patents pending

(51) Int. Cl.

(52) U.S. Cl.

H01G 4/20

H01G 4/10

H01G 4/02

H01B 3/16

(58) Field of Classification Search

(2006.01)

(2006.01)

(2006.01)

See application file for complete search history

(2013.01); H01G 4/02 (2013.01); H01G 4/10

H01G 4/20 (2013.01); H01B 3/16

. H01G 4/02; H01G 4/20

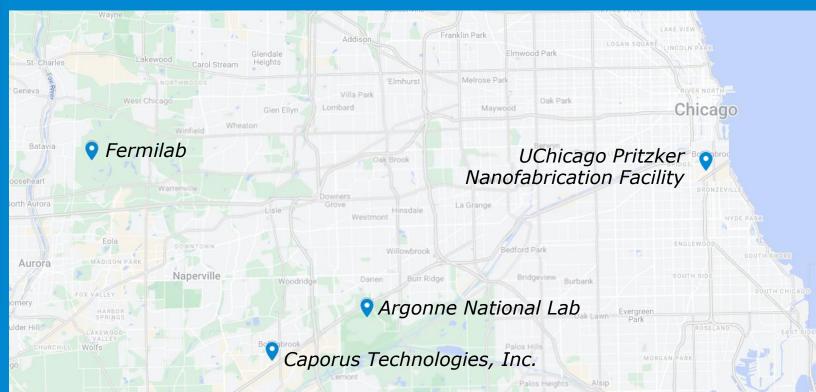

# Caporus is located near Fermilab and Argonne in Southwest Chicagoland

Caporus was previously embedded at Argonne through the Chain Reaction Innovations program. Operations are headquartered between Argonne and Fermilab.

Caporus Technologies, Inc.

# Intro to Caporus & NLP™

# Silicon on Insulator for NP

Phase II Demonstration

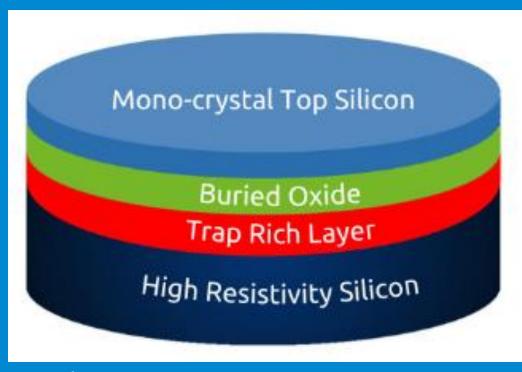

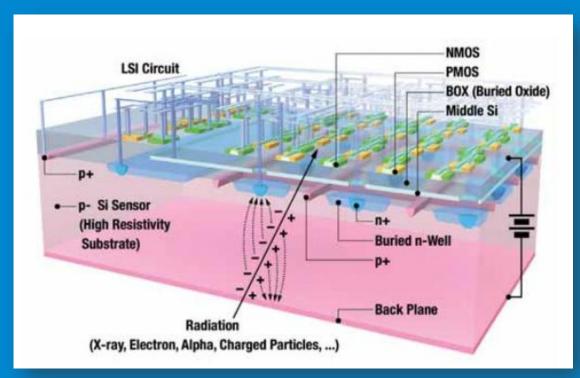

# Silicon on Insulator (SOI)

#### Commercial RF-SOI Substrate Structure

Image from SOITEC

| SOI Advantages         | SOI Disadvantages             |

|------------------------|-------------------------------|

| Superior Single Event  | Total Ionizing Dose Issues    |

| Upset Tolerance        | (Charge Effects)              |

| Better Noise Isolation | Radiation Damage to BOX       |

| Speed                  | Back-gate Effect due to Field |

|                        | Applied in Sensor             |

| Density                | Coupling of Charges in BOX    |

|                        | and sensor                    |

# Improved SOI for MAPS

- Reduce unwanted coupling between substrate and front-end electronics

- Reduced back-gate effect

- Improve sensitivity

- Reduce noise

- Elimination of inversion layer effects

- Enable depletion with applied electric field

- Improve sensitivity

- Improved radiation hardness

- Lower radiation cross-section

- Reduced coupling decreases effects of trapped charges

SOIPIX - 2016 KEK Annual Report

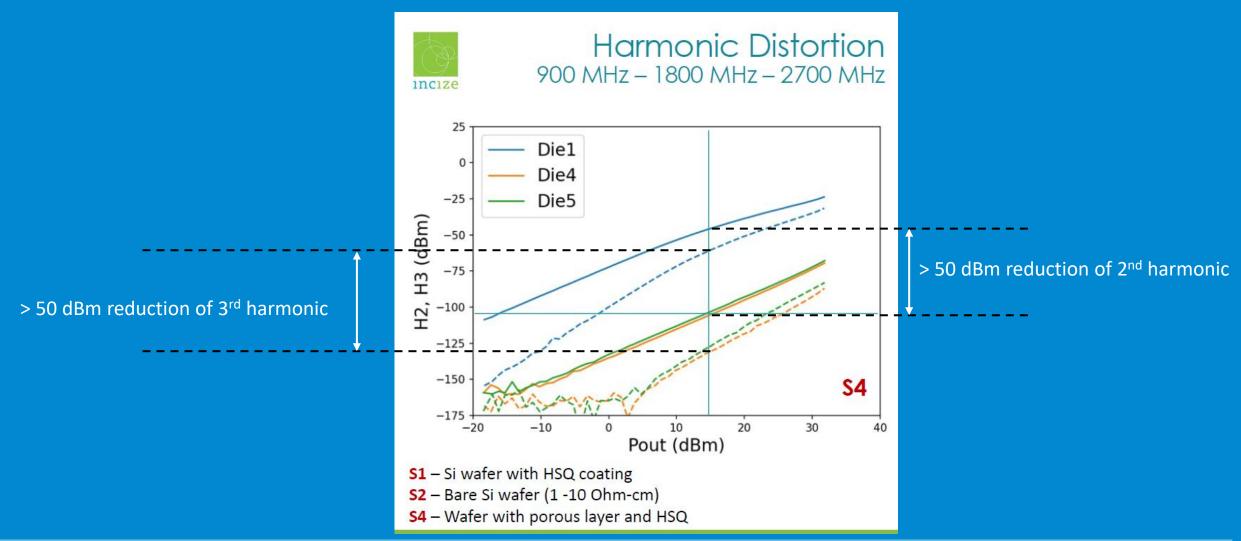

# Early Development - Third-Party RF Testing 🔀 ⊂

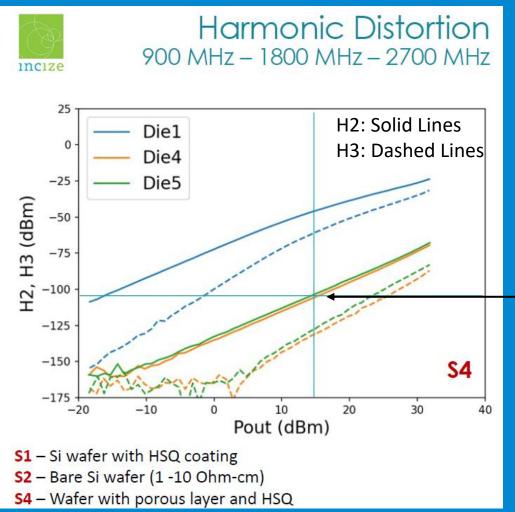

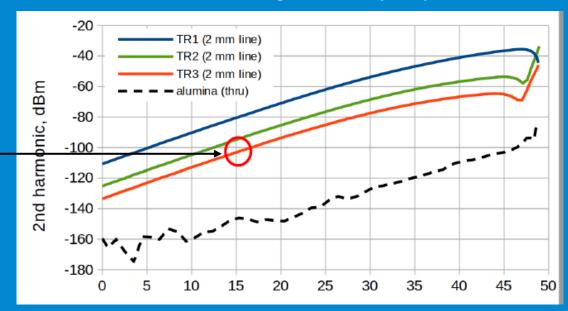

Third-Party testing has verified > 50 dBm reduction in 2<sup>nd</sup> and 3<sup>rd</sup> harmonic distortion through the addition of Caporus' porous materials.

Caporus Technologies, Inc.

# Early Development - Third-Party RF Testing 🔀 CAPO

### Demonstrated Performance with Lower Cost Substrates

Wafers Without (Blue) and With (Green) Caporus' Porous Layer

#### Current State-of-the-Art High Resistivity, Trap-Rich Wafers

# Intro to Caporus & NLP™

# Silicon on Insulator for NP

Phase II Demonstration

## Phase II Project Summary

- Priorities from Solicitation

- Next generation of monolithic active pixel sensors (MAPS)

- Radiation hardness (EIC luminosity of 10<sup>33</sup> 10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup>)

- Apply E-field to substrate to fully deplete detection volume

- Proposed Technology

- Implement MAPS on SOI

- Improved single-event upset, better noise isolation, speed, and density compared to bulk process

- Modified SOI with porous Si below BOX

- Reduce capacitive coupling between Si layers (Lower  $\varepsilon_{eff}$  and greater non-BOX thickness of porous Si)

- Reduce trapped charge in BOX with modified substrate

- Eliminate parasitic conduction layer at interface of BOX and bulk Si (Trap-rich)

- Phase II Demonstration

- 1. Scale processes for radiation testing

- 2. Etching processes for porous layer

- 3. Design CMOS and test structures

- 4. Fabricate test devices

- 5. Test for radiation hardness

- With and without proprietary modification

- Before and after irradiation

### Phase II Resources

#### **Phase II Team**

- Caporus Technologies

- Kevin O'Connor (PI)

- Nikki Chang

- Karabi Mondal

- Eric Acosta

- Bill Fortino

- Michael Boehme

- Jim Cable (Consultant SOI Development and Commercialization)

- Francis Chapman (Consultant Materials Development)

- Subaward

- Fermi National Accelerator Laboratory

- Xiaoran Wang, Farah Fahim, Davide Braga (SOI MAPS Design, Irradiation, Device Testing)

### **Additional Resources**

- Foley and Lardner (TABA)

- IP: USPTO and PCT applications

- Contracts: Commercial engagement pilot and license

- External Facilities

- Argonne Center for Nanoscale Materials (CNM)

- UChicago Pritzker Nanofabrication Facility

- Northwestern Medicine Proton Center

- Carl Traynor (Consultant Commercialization)

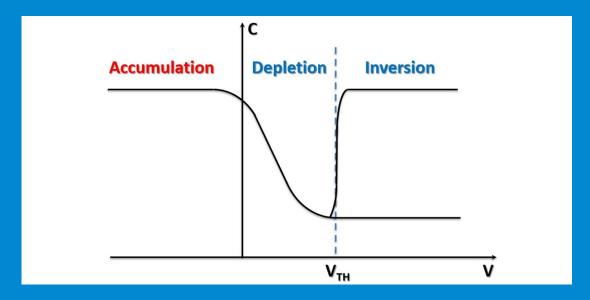

## Radiation Testing: MOS Capacitor

### **MOS Capacitor**

- C-V sweep

- Accumulation, depletion, and inversion

- Identify flatband voltage, threshold voltage

Measurements are sensitive to trapped charge in the oxide

- Shift in the C-V curve enables comparison of ionization radiation damage due to trapped charge accumulation

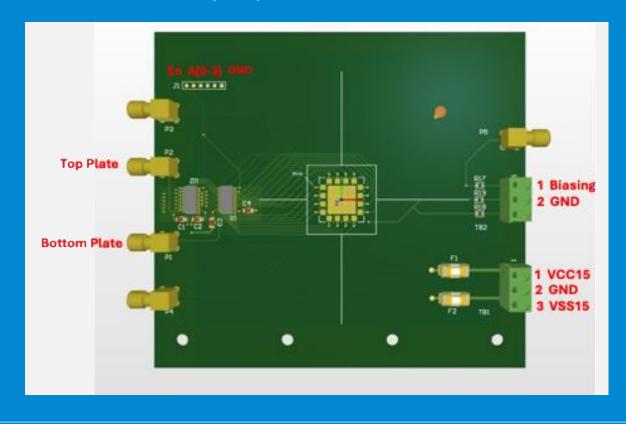

## Radiation Testing: MOS Capacitor

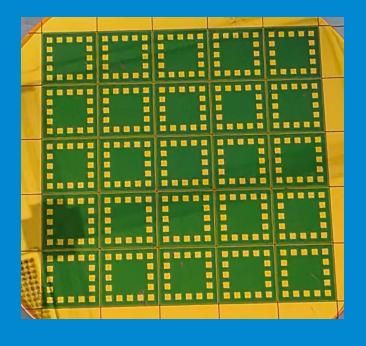

### **SOI Dies**

- 16 MOS capacitors per die

- Common proprietary modification for all 16 devices per die

- 4 implementations of porosity across all dies

- Fabricated by Caporus

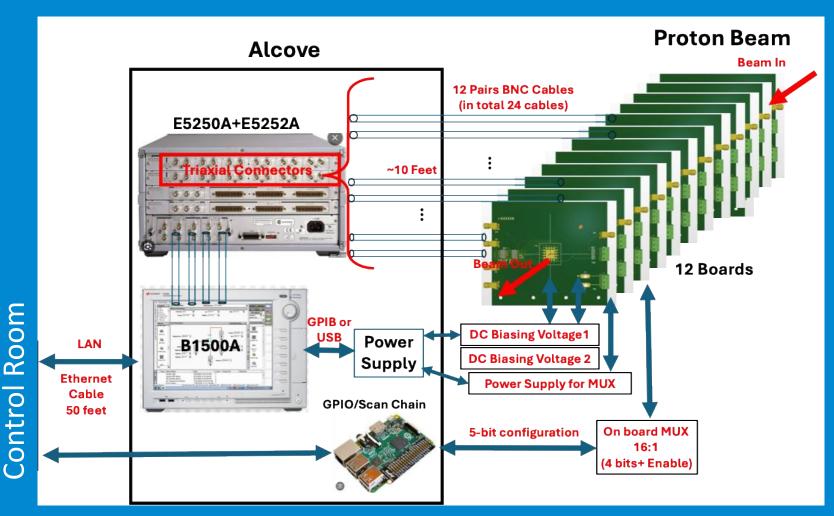

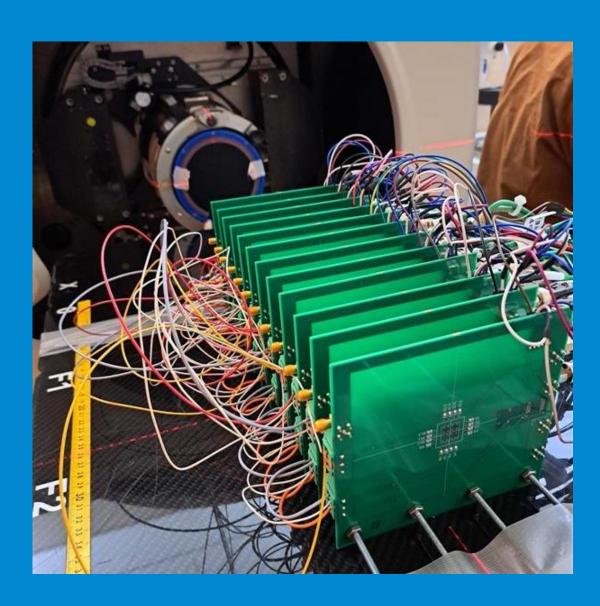

### Test Boards

- 1 SOI die per board

- Onboard multiplexer selects between 16 devices

- Single bias voltage per board

- Fabricated by Fermilab

# Radiation Testing: MOS Capacitor

### **Test Setup**

- 12 test boards

- 4 die variations

- 3 bias voltages (0, 10, and 15 V)

- 192 total devices under test

### Measurement System

- Keysight B1500A

- C-V sweep

- 1 kHz 5 MHz

- E5250A + E5252A

- Select between the 12 boards

Test and measurement lead by Fermilab

## Radiation Testing: 7/26 Tests

### Testing at Northwestern Medicine Proton Center

- 175 MeV protons

- 1E9 p/cm<sup>2</sup>/s

- Planned for 300 mins for 1 Mrad TID

- Completed first 60 mins (~200 krad) before proton center staff cancelled remaining radiation

- Post-radiation electrical measurements pending

## Asks from NP Community

- Recommendations for radiation testing sources

- Continued availability and suitability of the Northwestern Proton Center is unknown

- Would testing with other radiation sources be more valuable to the NP community?

- Next steps

- Complete measurements from 7/26 prototype irradiation

- Conduct 2<sup>nd</sup> round of TID measurements (NCTE)

Contact

PI: Kevin O'Connor

oconnorka@caporus.com