**Future High Performance Computing Capabilities**

Summary Report of the Advanced Scientific Computing Advisory Committee (ASCAC) Subcommittee (DRAFT VERSION — NOT FOR DISTRIBUTION)

December 19, 2017

# Contents

| 1        | Exe  | cutive Summary                                                               | 1         |

|----------|------|------------------------------------------------------------------------------|-----------|

| <b>2</b> | Bac  | kground                                                                      | 4         |

|          | 2.1  | Moore's Law and Current Technology Roadmaps                                  | 4         |

|          | 2.2  | Levels of Disruption in Post-Moore era                                       | 6         |

|          | 2.3  | National Landscape for Post-Moore Computing                                  | 7         |

|          | 2.4  | International Landscape for Post-Moore Computing                             | 7         |

|          | 2.5  | Interpretation of Charge                                                     | 8         |

| 3        | App  | olication lessons learned from past HPC Technology Transitions               | 9         |

|          | 3.1  | Background                                                                   | 9         |

|          | 3.2  | Vector-MPP Transition                                                        | 9         |

|          | 3.3  | Terascale-Petascale Transition                                               | 10        |

|          | 3.4  | Petascale-Exascale Transition                                                | 11        |

|          | 3.5  | Lessons Learned                                                              | 11        |

|          | 3.6  | Assessing Application Readiness                                              | 12        |

|          | 3.7  | Next Steps                                                                   | 12        |

| 4        | Fut  | ure HPC Technologies: Opportunities and Challenges                           | <b>14</b> |

|          | 4.1  | Reconfigurable Logic                                                         | 14        |

|          | 4.2  | Memory-Centric Processing                                                    | 16        |

|          | 4.3  | Silicon Photonics                                                            | 18        |

|          | 4.4  | Neuromorphic Computing                                                       | 22        |

|          | 4.5  | Quantum Computing                                                            | 24        |

|          | 4.6  | Analog Computing                                                             | 26        |

|          | 4.7  | Application Challenges                                                       | 27        |

|          | 4.8  | Open Platforms                                                               | 28        |

| <b>5</b> | Fine | dings                                                                        | 29        |

|          | 5.1  | Need for clarity in future HPC roadmap for science applications              | 29        |

|          | 5.2  | Extreme heterogeneity with new computing paradigms will be a common theme in |           |

|          |      | future HPC technologies                                                      | 29        |

|          | 5.3  | Need to prepare applications and system software for extreme heterogeneity   | 30        |

|          | 5.4  | Need for early testbeds for future HPC technologies                          | 30        |

|          | 5.5  | Open hardware promises to be a major trend in future platforms               | 30        |

|          | 5.6  | Synergies between HPC and mainstream computing                               | 30        |

Future High Performance Computing Capabilities

| 6            | Recommendations                                                       | <b>32</b> |

|--------------|-----------------------------------------------------------------------|-----------|

|              | 6.1 Office of Science's Role in Future HPC Technologies               | 32        |

|              | 6.2 Investing in Readiness of Science Applications for post-Moore era | 32        |

|              | 6.3 Investing in Research related to Open Hardware Platforms          | 33        |

|              | 6.4 Investing in Research related to System Software                  | 34        |

|              | 6.5 Early Testbeds in DOE Computing Facilities                        | 34        |

|              | 6.6 Recruiting, Growing and Retaining Talent for post-Moore era       | 35        |

| 7            | Conclusions                                                           | 36        |

| $\mathbf{A}$ | Charge to Subcommittee                                                | 37        |

| в            | Subcommittee Members                                                  | 38        |

| $\mathbf{C}$ | Bibliography                                                          | 39        |

# List of Figures

| 2.1 | 40 years of Microprocessor Trend Data for 1) Number of Transistors, 2) Single Thread   |    |

|-----|----------------------------------------------------------------------------------------|----|

|     | Performance, 3) Frequency, 4) Power, 5) Number of Cores                                | 5  |

| 2.2 | Levels of disruption in the computing stack, from [1]                                  | 6  |

| 4.1 | Growing an ecosystem for Amazon EC2 F1 FPGA instances (image source: https:            |    |

|     | <pre>//aws.amazon.com/ec2/instance-types/f1)</pre>                                     | 15 |

| 4.2 | Different levels of memory-centric processing                                          | 18 |

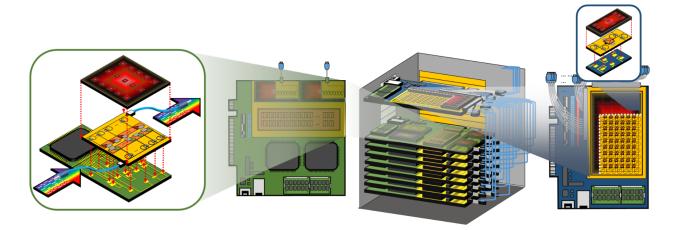

| 4.3 | Current photonic interconnect technologies                                             | 20 |

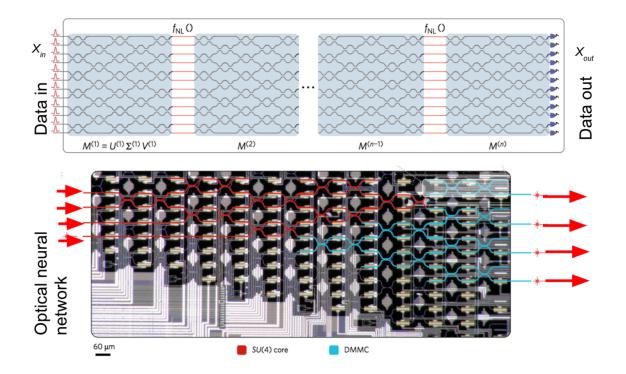

| 4.4 | The optical NN consists of a series of n layers, each consisting of a matrix transfor- |    |

|     | mation M followed by an optical nonlinearity. The computation on an input vector       |    |

|     | Xin, encoded in the amplitudes of laser signals (left), occurs nearly instantaneously  |    |

|     | at the speed of light.                                                                 | 23 |

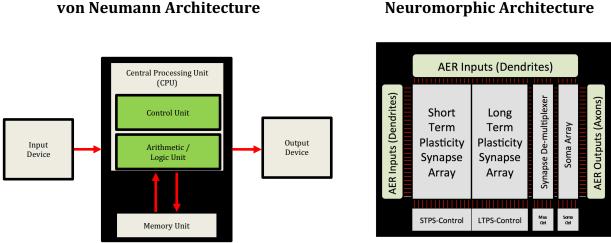

| 4.5 | Comparison between conventional and neuromorphic computer architectures                | 23 |

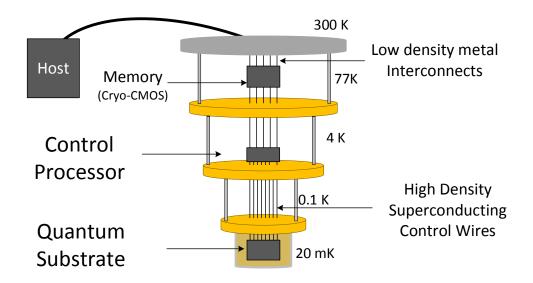

| 4.6 | Thermal hierarchy for host and control processes connected to a quantum substrate      | 25 |

# List of Tables

| 2.1 | Projections for the continuation, and end, of Moore's Law during the next 15 years (Source: IEEE IRDS 2017 Edition).                                                                                                                                                                                                                                                                 | 5  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | This table shows a simple illustration using sparse linear solvers as the target prob-<br>lem. For all von Neumann technologies, this is a good target problem. For non-von<br>Neumann architectures, linear solvers do not have a clear mapping. In fact, alterna-<br>tive algorithms are most likely required, or the need to solve a linear system may be<br>bypassed completely. | 13 |

| 4.1 | Performance characteristics for different levels of memory-centric processing                                                                                                                                                                                                                                                                                                        | 17 |

### Chapter 1

## **Executive Summary**

The ASCAC Subcommittee on Future High Performance Computing (HPC) Capabilities has reviewed opportunities and challenges related to the most promising technologies that are currently planned for the post-exascale (2020's) and post-Moore (2030's and beyond) timeframes. We briefly summarize below the key findings and recommendations from this review, from the perspective of planning and research directions that need to be given priority to prepare for the very significant challenges that await us in the post-Moore computing era. An overarching concern that emerged from the subcommittee's deliberations is that DOE has lost considerable momentum in funding and sustaining a research pipeline in the applied math and computer science areas that should have been the seed corn for preparing for these future challenges, and it is therefore critical to correct this gap as soon as possible. While the subcommittee understands the paramount importance of DOE's commitment to deliver exascale capabilities, we believe that it is essential for DOE ASCR to fund research and development that looks beyond the Exascale Computing Project (ECP) time horizon so as to ensure our nation's continued leadership in HPC.

Finding 1: Need for clarity in future HPC roadmap for science applications. The challenges associated with post-exascale and post-Moore computing are receiving significant attention from multiple government agencies and initiatives including DARPA, IARPA, NSF and NSCI. The subcommittee believes that Science will need to be prepared for a period of uncertainty in future HPC technologies and computing paradigms, and that, because of this uncertainty, there is a need to focus on strategy and planning activities so as to better anticipate what the future HPC roadmap possibilities will be for science applications.

Finding 2: Extreme heterogeneity with new computing paradigms will be a common theme in future HPC technologies. As discussed in the report, there is a great diversity in the technologies that are expected in the post-exascale and post-Moore eras, which has been appropriately labeled as "extreme heterogeneity" in an upcoming ASCR workshop and related discussions. The subcommittee believes that there is value in focusing on extreme heterogeneity as a common theme in future HPC technologies, so as to enable a broader view of post-Moore computing rather than focusing solely on point solutions.

Finding 3: Need to prepare applications and system software for extreme heterogeneity. As discussed in the report, different applications have responded to past technology transitions (e.g., from vector to MPP, terascale to petascale, petascale to exascale) in different ways. We are rapidly approaching a period of significant redesign and reimplementation of applications that is expected to surpass the disruption experienced by the HPC community when transitioning from vector to MPP platforms. As a result, scientific teams will need to prepare for a phase when they are both using their old codes to obtain science results while also developing new application frameworks based on the results of applied math and computer science research investments that need to be made now. High-quality design and implementation of these new frameworks will be crucial to the future success of DOE computational science.

Finding 4: Need for early testbeds for future HPC technologies. Given the wide diversity of technologies expected in the post-Moore era, accompanied by radically new computing paradigms in many cases, there is a need for building and supporting early testbeds for future HPC technologies that are broadly accessible to the DOE community, so as to enable exploration of these technologies through new implementations of science (mini-)applications.

Finding 5: Open hardware promises to be a major trend in future platforms With extreme heterogeneity, there is a growing trend towards building hardware with open interfaces so as to integrate components from different hardware providers. There is also a growing interest in building "open source" hardware components through recent movements such as the RISC-V foundation. For the purpose of this report, the term "open hardware" encompasses both open interfaces for proprietary components as well as open source hardware components.

Finding 6: Synergies between HPC and mainstream computing Though this report has focused on future high performance computing requirements from the perspective of science applications, there are notable synergies between future HPC and mainstream computing requirements. One application area where these synergies are already being leveraged, and will undoubtedly grow in the future, is in the area of data-intensive applications and data analytics (e.g., the use of neuromorphic computing and other accelerators for deep learning).

**Recommendation 1: Office of Science's Role in Future HPC Technologies.** The findings in this study have identified the urgency of developing a strategy, roadmap and plan for high performance computing research and development in the post-exascale and post-Moore eras, so as to ensure continued advancement of Science in the future. Though there are multiple government agencies that are stakeholders in post-Moore computing, the subcommittee recommends that the DOE Office of Science play a leadership role in developing a post-Moore strategy/roadmap/plan for advancing high performance computing in the service of Science.

**Recommendation 2:** Investing in Readiness of Science Applications for post-Moore era. The findings in this study have identified the challenges involved in preparing applications for past technology disruptions, and the fact that future disruptions will require exploration of new computing paradigms as we move to extreme heterogeneity in the post-exascale and post-Moore computing eras. The subcommittee recommends that the Office of Science work with other offices of DOE to ensure that sufficient investment is made with adequate lead time to prepare science applications for the post-Moore era. While the adaptations that ECP application teams are starting to make for supporting current and emerging heterogeneous execution environments is good preparation for some of the anticipated post-exascale technologies, additional investments will be needed to explore the newer computing paradigms that will emerge in the post-exascale and post-Moore timeframes. In addition, we recommend that R&D in best practices for design and development of scientific software be given high priority to best assure that new scientific application frameworks benefit from the state of the art in software best practices.

**Recommendation 3:** Investing in Research related to Open Hardware Platforms. The findings in this study have identified the need for creating a more open hardware ecosystem in the post-exascale and post-Moore eras, relative to current and past approaches for hardware acquisition. In the interest of future Science needs, the subcommittee recommends that the Office of Science foster this ecosystem by investing in research related to open hardware platforms, i.e., platforms built using open interfaces that support high-performance and reliable integration of components from different hardware providers.

**Recommendation 4: Investing in Research related to System Software.** The findings in this study have identified the need for advancing system software to meet the requirements of post-Moore computing. The DOE should support active and sustained efforts to contribute to relevant software projects to ensure that HPC concerns such as performance isolation, low latency communication, and diverse wide area workflows are addressed in the design and adoption of system software for future HPC platforms.

**Recommendation 5: Early Testbeds in DOE Computing Facilities.** The findings in this study have identified the need for providing users of DOE computing facilities early access to testbeds and small-scale systems that are exemplars of systems expected in the post-Moore computing roadmap. The subcommittee recommends that the Office of Science's computing facilities address this need by acquiring such testbeds and small-scale systems, and providing and supporting access to these systems by current HPC users.

**Recommendation 6:** Recruiting, Growing and Retaining Talent for post-Moore era. The findings in this study have identified the need for significant innovation in support of the enablement of science applications on post-Moore hardware. The subcommittee recommends that DOE national laboratories prioritize the recruiting and nurturing of top talent in all aspects of mapping applications onto emerging post-Moore hardware, including skills and talent related to development of science applications, applied mathematics research, system software research, and hardware research for future platforms.

### Chapter 2

## Background

#### 2.1 Moore's Law and Current Technology Roadmaps

Moore's Law [2,3] has been the bedrock for growth in the capabilities of all computing systems, including high performance computing (HPC) systems. Simply stated, Moore's Law is the prediction that the number of transistors (components) in an integrated circuit would double approximately every two years. The significance of Moore's Law is that the semiconductor industry has strived to maintain this exponential growth for over five decades, resulting in important benefits in cost and performance for all semiconductor consumers. The cost implication of Moore's Law is that if the cost of an integrated circuit remains approximately constant, then the cost per transistor decreases exponentially with time. The performance implication of Moore's Law used to relate to Dennard Scaling [4], which stated that, as transistors become smaller, their power density remains constant, i.e., the power consumed by an integrated circuit remains proportional to the area of the circuit rather than the number of transistors in the circuit. An underlying assumption behind the Dennard Scaling prediction is that the power consumed by an integrated circuit is dominated by its dynamic (switching) power, which in turn is proportional to the clock frequency. As a result, when Dennard Scaling holds, the power per transistor decreases exponentially with time, which in turn made it possible to increase clock frequencies from generation to generation of a semiconductor technology without increasing the total power consumed by the integrated circuit.

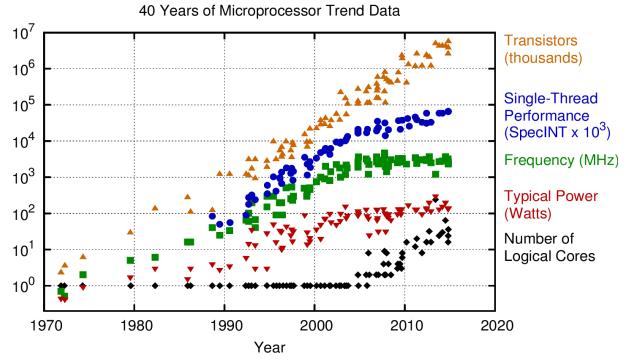

One of the major challenges recently faced by the computing industry is the fact that Dennard Scaling ended over a decade ago, as shown in Figure 2.1, which includes trend data for microprocessors built during the last 40 years. (Note that the y-axis numbers are plotted on a logarithmic scale.) The first observation from the figure is that Moore's Law has remained robust during this period, since the number of transistors in a microprocessor continued to increase at an exponential rate until the present time. However, the clock frequencies flattened in the 1 GHz (=  $10^3$  MHz) range since around 2005, thereby signalling the end of Dennard Scaling. The main reason for this end is that the leakage power started becoming a significant component of the power consumed by transistors, as the transistor sizes decreased. Past 2005, any attempt to increase clock frequency became impractical because doing so would cause the chip to overheat. Instead, 2005 marked the start of the "multicore era" in which the additional transistors predicted by Moore's Law are being used to increase the number of processor cores in a single integrated circuit, without increasing their clock frequencies.

If Moore's Law were to continue indefinitely, we could continue getting more performance from successive generations of semiconductor technology by doubling the number of processor cores in an integrated circuit rather than by increasing the clock frequency. However, it stands to reason

Original data up to the year 2010 collected and plotted by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond, and C. Batten New plot and data collected for 2010-2015 by K. Rupp

Figure 2.1: 40 years of Microprocessor Trend Data for 1) Number of Transistors, 2) Single Thread Performance, 3) Frequency, 4) Power, 5) Number of Cores.

| Table MM01 - More Moore - Logic Core Device Technolog                     | y Roadmap            |                                 |                      |                   |                       |                                |                               |

|---------------------------------------------------------------------------|----------------------|---------------------------------|----------------------|-------------------|-----------------------|--------------------------------|-------------------------------|

| YEAR OF PRODUCTION                                                        | 2017                 | 2019                            | 2021                 | 2024              | 2027                  | 2030                           | 2033                          |

|                                                                           | P54M36               | P48M28                          | P42M24               | P36M21            | P28M14G1              | P26M14G2                       | P24M14G3                      |

| Logic industry "Node Range" Labeling (nm)                                 | "10"                 | "7"                             | "5"                  | "3"               | "2.1"                 | "1.5"                          | "1.0"                         |

| IDM-Foundry node labeling                                                 | i10-f7               | i7-f5                           | i5-f3                | i3-f2.1           | i2.1-f1.5             | i1.5-f1.0                      | i1.0-f0.7                     |

|                                                                           | finFET               | finFET                          | LGAA                 | LGAA              | VGAA                  | VGAA                           | VGAA                          |

| Logic device structure options                                            | FDSOI                | LGAA                            | VGAA                 | VGAA              | M3D                   | M3D                            | M3D                           |

| Logic device mainstream device                                            | finFET               | finFET                          | LGAA                 | LGAA              | VGAA                  | VGAA                           | VGAA                          |

|                                                                           |                      |                                 |                      |                   |                       |                                |                               |

|                                                                           | FinFET               | FinFET                          | Lateral Nanowire     | Lateral Nanowire  |                       | Vertical Nanowire              | Vertical Nanowire             |

| Logic device technology naming                                            |                      |                                 | Vertical Nanowire    | Vertical Nanowire |                       |                                |                               |

|                                                                           |                      |                                 |                      |                   |                       |                                |                               |

| Patterning technology inflection for Mx interconnect                      | 193i                 | 193i, EUV                       | 193i, EUV            | 193i, EUV         | 193i, EUV             | 193i, EUV                      | 193i, EUV                     |

| Channel material technology inflection                                    | Si                   | SiGe25%                         | SiGe50%              | Ge, IIIV (TFET)   | Ge, IIIV (TFET)       | Ge, IIIV (TFET)                | Ge, IIIV (TFE)                |

| Process technogy inflection                                               | Conformal deposition | Conformal<br>Doping,<br>Contact | Channel, RMG         | CFET              | Seq. 3D               | Seq. 3D                        | Seq. 3D                       |

| Stacking generation                                                       | 2D                   | 2D                              | 2D<br>3D: W2W or D2W | 3D: P-over-N      | 3D: SRAM-on-<br>Logic | 3D: Logic-on-<br>Logic, Hetero | 3D: Logic-on<br>Logic, Hetero |

| Design-technology scaling factor for standard cell                        | -                    | 1.11                            | 2.00                 | 1.13              | 0.53                  | 1.00                           | 1.00                          |

| Design-technology scaling factor for SRAM (111) bitcell                   | 1.00                 | 1.00                            | 1.00                 | 1.00              | 1.25                  | 1.00                           | 1.00                          |

| Number of stacked devices in one tier                                     | 1                    | 1                               | 3                    | 4                 | 1                     | 1                              | 1                             |

| Tier stacking scaling factor for SoC                                      | 1.00                 | 1.00                            | 1.00                 | 1.00              | 1.80                  | 1.80                           | 1.80                          |

| Vdd (V)                                                                   | 0.75                 | 0.70                            | 0.65                 | 0.60              | 0.50                  | 0.45                           | 0.40                          |

| Physical gate length for HP Logic (nm)                                    | 20.00                | 18.00                           | 14.00                | 12.00             | 10.00                 | 10.00                          | 10.00                         |

| SoC footprint scaling node-to-node - 50% digital, 35% SRAM, 15% analog+IO | -                    | 64.9%                           | 51.3%                | 64.3%             | 64.2%                 | 50.9%                          | 50.7%                         |

Table 2.1: Projections for the continuation, and end, of Moore's Law during the next 15 years (Source: IEEE IRDS 2017 Edition).

that Moore's Law must come to an end due to basic physical limitations, including the fact that the size of the atoms used in silicon chip fabrication is around 0.2nm. Table 2.1 shows the projected transistor size ("node range") decreasing from 10nm in 2017 to 1.0nm in 2033, at which point a single transistor would shrink to the size of five Silicon atoms. Further, achieving the reductions shown in Table 2.1 will require major technology advances, including monolithic 3D transistors expected from 2024 onwards. It is therefore clear that alternate computing technologies and paradigms urgently need to be explored for future HPC, to ensure the continued and sustained performance gains to which HPC users and customers are accustomed. Given this context, we will refer to the 2020's decade as "post-exascale" and the 2030's decade and beyond as "post-Moore" in this report.

#### 2.2 Levels of Disruption in Post-Moore era

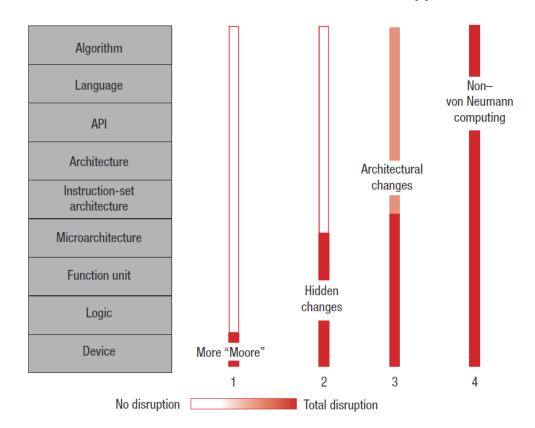

The IEEE Rebooting Computing Initiative [1] has characterized a range of possible approaches to address the end of Moore's law. As shown in Figure 2.2, these approaches can be classified in terms of the amount of disruption to the computing stack they would require [1].

Figure 2.2: Levels of disruption in the computing stack, from [1].

The least disruptive approach in Figure 2.2 is for the industry to find a drop-in replacement for the CMOS switch. Existing transistor technologies cannot be both power efficient and operate reliably at the scales at the end of the roadmap. Thus, this approach is to create a new transistor technology. Although this is the least disruptive approach to the computing stack, it is exceedingly challenging. The IRDS roadmap shows that Moore's Law will run out even with these new transistor types by 2033 [5].

The next least disruptive approach is to use novel ways to construct computer microarchitectures while still maintaining software compatibility to the existing software base. These include microarchitectures implemented using techniques such as some Silicon Photonics approaches (Section 4.3). Other approaches not discussed in this report include adiabatic/reversible logic and cryogenic/superconducting logic.

The next disruptive approach involves making architectural changes that are "programmer visible." Where these approaches will require new programming systems., they generally do not abandon the von Neumann computing paradigm. These approaches include Reconfigurable Logic 4.1, Memory-Centric Processing (Section 4.2), and some approaches that employ Silicon Photonics (Section 4.3), all of which are promising approaches for the post-exascale era.

The most radical (Level 4) approaches rethink computing paradigms from the ground up, and will require new algorithms, programming systems, system software, and hardware. Examples of this include Neuromorphic Computing (Section 4.4), Quantum Computing (see Section 4.5) and Analog/Thermodynamic Computing (Section 4.6). All of these represent potential candidates for the post-Moore era.

#### 2.3 National Landscape for Post-Moore Computing

Leadership in HPC is critical to the success of many Federal agencies, as well as that of many commercial enterprises; all these players are concerned about what the future portends beyond the end of Moore's Law. Many are investing, or planning to do so, and there is an opportunity for DOE to coordinate its efforts with them, so as to maximize the benefit to all. Where serious sustained investments are being made, DOE need not duplicate them. For example, IARPA is investing in both specialized analog quantum systems (QEO) and the foundations of general purpose devices (LOGIQ). IARPA is also exploring superconducting logic as the basis for classical computing (C3). DARPA MTO is developing a new research initiative targeting an electronics resurgence, and at this early stage, DOE can perhaps influence directions that can have synergistic benefits with science applications. MTO is already investing in HPC related technologies such as hybrid analog and digital systems (ACCESS), design automation (CRAFT), IP reuse (CHIPS), integrated photonics (POEM), and energy efficiency (PERFECT). And, of course, many commercial enterprises are investing in the development of special-purpose accelerators for deep learning and related AI algorithms and applications.

A key point underlying all the activities under way in other agencies and commercial entities is that, while they may not be directly working on advancing HPC for science applications, they are investing in technologies that could be highly relevant to DOE's future HPC roadmap for science. It is also worth noting that the NSCI has designated DOE as playing the leadership role for HPC. Therefore, DOE has a unique opportunity to not only explore the future of HPC for scientific leadership, but to also determine if the broader HPC technology investments in the US government are adequate to enhance and sustain the economy and security of the US as has been done by past investments in computing technologies.

#### 2.4 International Landscape for Post-Moore Computing

In late 2013, IEEE launched the international IEEE Rebooting Computing Initiative (IEEE RCI) to begin to look at potential post-Moore computing possibilities [1]. Since that time, IEEE RCI has held four invitational summits of thought leaders across multiple fields. The IEEE RCI sponsors the International Conference on Rebooting Computing (ICRC), now in its second year (2016 was its

inaugural year). ICRC attracts researchers from around the globe to share their best post-Moore computing ideas.

In 2016, the Semiconductor Industry Association pulled its sponsorship for the venerable International Technology Roadmap for Semiconductors (ITRS). IEEE moved swiftly to become the new sponsor of the roadmap. To give the roadmap a post-Moore viewpoint, two new focus teams were added, one to track application performance and one to track architectural ideas. The IEEE renamed the roadmap the *International Roadmap for Devices and Systems* (IRDS) in part to avoid copyright concerns, but moreover to stress the changing nature of the industry towards post-Moore technology considerations [1]. IRDS partner organizations include the Japan Physics Society's *Systems and Devices Roadmap for Japan* (SDRJ) and the EU's *NanoElectronics Roadmap for Europe: Identification and Dissemination* (NEREID). IRDS produced a roadmap at the end of 2017 and will continue the ITRS' historic cadence of a new roadmap every two years, with a roadmap update in the intervening years [5].

Finally, subcommittee members are aware of recent announcements from China, Europe and Japan related to Quantum Computing and Neuromorphic Computing that foretell a high level of international competitiveness in the post-Moore Computing era.

#### 2.5 Interpretation of Charge

The subcommittee appreciated the timeliness of the charge, a copy of which is included in Appendix A. At the same time, we acknowledge that a single study cannot provide a comprehensive answer to identifying research opportunities and challenges for future HPC capabilities in the post-exascale and post-Moore timeframes, which span multiple decades. We trust that there will be follow-on studies to elaborate further on these challenges and opportunities as details of emerging HPC technologies become clearer in the coming years. To focus our efforts in this study, we made the following two assumptions when interpreting the charge:

- There are multiple Federal government initiatives and programs in the early stages of addressing the challenges of post-Moore computing. The subcommittee explicitly restricted the scope of this study to considerations pertinent to the use of computing for the advancement of Science, thereby focusing on the Office of Science's mission needs, while still identifying synergies with strategic needs of other government agencies and commercial endeavors.

- The charge did not specify a timeframe to be assumed for our recommendations, though it was clear that the charge refers to timeframes that follow the accomplishment of exascale capability in the DOE. The subcommittee concluded that it was appropriate to focus on different timeframes for different technologies, based on their anticipated levels of readiness. These timeframes include the post-exascale (2020s) and post-Moore (2030s and beyond) eras mentioned earlier.

### Chapter 3

# Application lessons learned from past HPC Technology Transitions

#### 3.1 Background

All HPC technology transitions have been focused on algorithm and application designs that expose more concurrency and locality. The advent of vector supercomputers such as the Control Data Cyber 205 and Cray 1 were notable early examples. Application developers organized data and computations to expose unit stride memory accesses and conflict-free writes that could be written as Q8 function calls on the Cyber 205, or converted to Cray vector instructions by the compiler. Clock speed improvements and improved functional parallelism (simultaneous execution of instruction streams) were very important for performance improvements from one generation of machines to another, and had the advantage of not forcing substantial application refactoring to realize those benefits.

Disruptive transitions occurred when the fundamental strategy for organizing data and computations changed. Vector supercomputing applications represented the first large body of optimized applications where the data and computation strategies were specialized to match a particular parallel computing model. Multiprocessing vector computations were also important, but few codes were explicitly organized to exploit multiple vector processors, relying instead on shared memory fork-join models that required minimal code modifications. The first Gordon Bell Prize was given for a auto-tasked, vectorized version of a multifrontal, super-nodal sparse direct solution on an 8-processor Cray Y-MP, but, practically speaking, the best use of multiple Cray vector processors was to improve job throughput of single processor vector codes.

#### 3.2 Vector-MPP Transition

The large body of vector HPC applications developed in the 1980s and early 1990s represented a valuable collection of HPC capabilities. While IBM mainframes had caches and CDC memory-tomemory vector computers enabled optimization-focused coding, Cray systems were available long enough to allow the HPC community an opportunity to create a large number of highly optimized codes for defense, engineering, weather, chemistry, oil & gas applications, and more. Many of these codes were large and full-featured. The arrival of Massively Parallel Processing (MPP) computers, which relied on a very different data and computation organization, represented a challenge to developers of vector applications. There was no incremental transition path from a shared memory vector design to a distributed memory MPP design. Many vector codes did not make the transition to MPP. For those that did, the most successful transitions started by first designing a new application framework specifically for distributed memory. Typically the framework partitioned logically global objects such as grids for PDE calculations into distributed subgrids with halos, and then provided halo exchange functions that would update halo values when called. The framework also provided reduction operations such as distributed dot products.

Given such frameworks, most of the computations that were part of the vector code could be migrated into the new with minimal changes. Assuming the halo exchange operation had been called to exchange remote values, halos enabled most computations to work with local data, just as before. Local reductions now needed a single new step to compute the global reduction. It is also worth noting that vectorization was not important for early MPPs. Maintaining vectorizable code is difficult because its presence is ubiquitous and often requires special design considerations. Without regular testing, vectorization impediments were introduced as new features are added to the code. In most MPP codes, vectorization features were not maintained, and eventually removed, especially as cached data access became more important.

The transition from vector computing to MPP was very challenging because constructing the new MPP framework took substantial time (months or years), during which the previous vector code had to remain the production platform, and the development team was split across two codes. Many vector codes were eventually retired as new MPP code emerged.

#### **3.3** Terascale-Petascale Transition

The Terascale to Petascale transition has been less disruptive overall. For most applications this transition was incremental in the sense that the MPP framework remained valid. Certainly, the framework had to be refined and scalability bottlenecks removed, as the number of distributed processors and the partitioning of data increased. But there was no disruptive ramp-up phase as was the case in the vector to MPP transition.

The path to Petascale included the introduction of small scale threading (e.g., using OpenMP threading with a modest number of cores), use of GPU accelerators, and exposing vectorizable code to compilers. But these features did not force a complete redesign for most codes. Instead, application developers had to incrementally refactor the most important computational kernels to run well and could leave much of less intensive code untouched. One notable exception was the disruptions incurred for migrating applications to the petascale RoadRunner computer, which were more extensive than for other (later) petascale systems. However, it can also be argued that the application changes needed for the RoadRunner system may have served as good preparation for the multi-GPU on-node parallelism (as an example) that needs to be exploited on exascale systems.

The approach used for terascale to petascale continues to be very effective, even as we go beyond petascale. In fact, it is the primary strategy used to port applications to the current fastest LINPACK machine, the Sunway TaihuLight. This system has thousands of distributed memory nodes that can be used as a large Linux cluster by mapping execution to just the Management Processing Elements (MPEs). Porting any MPP code to the MPE processors of the TaihuLight platform is very straightforward if the code is designed to run on scalable Linux clusters. Performance of the initial port is very poor, since the MPEs represent a tiny fraction of the system performance. But once the code is working on the MPEs, incremental porting of functionality to the CPEs (8x8 processor mesh) is possible, and is very similar to porting strategies use for GPU offloading. Certainly, very substantial data structure and execution strategy changes are required, but again an incremental approach is possible.

#### 3.4 Petascale-Exascale Transition

The petascale to exascale transition is currently under way. So far, the terascale to petascale approach is working well as a starting point for the petascale to exascale transition. At the same time, the applications that have been successful using this approach are typically highly structured and compute-intensive, but have still not achieved uniformly high performance across all the problem formulations that they are designed to handle. Furthermore, they are not prepared for simultaneous heterogeneous execution, where subproblem sizes must vary to tune for optimal performance on different processor types, nor is there sufficient on-node control of data partitioning and mapping, or concurrent execution of heterogeneous tasks. The DOE Trinity platform, with an equal number of Haswell and Knights Landing nodes requires exactly this kind of flexibility in order to simultaneously use both halves of the system.

In order to bring a full portfolio of applications to the exascale threshold, and to bring all applications forward beyond exascale, we face another disruptive phase. The growth of on-node concurrency, the need to execute concurrently on multiple heterogeneous nodes, and the increasing penalty for having any sequential execution regions in our codes mean we are on the front end of a new transition. While there is much research required, early indications are that we need to introduce new control layers and system software support (e..g., to support asynchronous tasking), that will enable us to better handle simultaneous heterogeneous execution, support task-enabled functional parallelism and latency hiding, and move toward an effective strategy for implementing application-level resilience capabilities.

#### 3.5 Lessons Learned

A summary of some of the key lessons learned from the three transitions summarized above is as follows:

- Vector-MPP: Investing in new application frameworks, built using results from related Applied Math and Computer Science research, was critical for success in this transition.

- Terascale-Petascale: Leveraging incremental approaches to application migration can be extremely valuable, when possible to do so.

- Petascale-Exascale: Investing in new control layers and system software support (e.g., for asynchronous heterogeneous tasking and data movement) is helpful for addressing the disruption of large on-node heterogeneous parallelism.

The HPC community has been gaining experience with increasingly diverse computing architectures. Heterogeneous architectures, first broadly encountered with attached GPUs (e.g., Titan), and now present on the TaihuLight and Trinity platforms have exposed application developers to the demands that we must address. In particular, our application designs and base implementations must lend themselves to rapid adaptation to new node architectures and flexible execution models. Use of discrete devices has also taught us important lessons of shipping computation to data and managing remote resources.

In addition, code teams are migrating to new languages as opportunities arise. For example, several Exascale Computing Project codes that were formerly Fortran or C based, e.g., NWChemEx and SLATE, have moved to C++. Teams report that C++ enables more rapid code development and improved adaptability, and many programming model research projects now offer C++ library interfaces as a primary parallel programming interface for scientific application developers.

Even so, we have much to learn about software design. Porting existing codes to new platforms can require a monumental effort, or can be designed into the code. An example of the former is the recent Gordon Bell finalist paper on porting the DOE climate CAM-SE dynamical core code to TaihuLight [6]. The authors reported that the effort required modification of 152,336 of the original 754,129 lines of code (20%), and the addition of 57,709 new lines (8% increase). While this porting effort was incremental, it is still very expensive. In contrast, the Uintah application [7] is coded using C++ with template meta-programming techniques that enable compile time mixing of platform-specific adaptations to general parallel pattern expressions. This approach enables support of many node types from the same source, including simultaneous heterogenous execution on more than one type.

#### **3.6** Assessing Application Readiness

The lessons learned from past technology transitions confirm that mapping applications to new platforms can be costly and risky. Most computational scientists are focused primarily on the new scientific insights that can be achieved through computation. Combined with the competition to produced new scientific results on a regular cadence, few computational scientists are prepared to take on the risk of migrating applications to new computing paradigms, unless absolutely necessary.

We briefly present an exemplar scorecard framework that can be used to assess application readiness for new computing platforms and paradigms. Table 3.1 lists attributes can be used to assess and prioritize scientific problems that would be good early targets for future HPC systems. A high rating in all areas indicates strong likelihood of success as an early adopter. The goal of this kind of analysis is to identify a first list of priority research directions for each target computing approach. The contents of the table include a simple illustration using sparse linear solvers as a target problem.

#### 3.7 Next Steps

We believe that recent experiences with preparing applications for emerging heterogeneity will also help with preparations for some of the post-exascale technologies in Chapter 4, though new challenges remain for post-Moore technologies. A good resource for any software refactoring effort is the book entitled "Working Effectively with Legacy Code" by Michael Feathers [8]. This book provides a practical step-by-step approach to planning and executing changes in an existing code for any purpose. Fundamental to the effort is covering the code that will be refactored with adequate regression testing. The scope of change should be incremental when possible, making sure that one change set is fully integrated and testing before starting the next.

Of course, the disruptive transition required to introduce a tasking control layer and supporting system software between the current MPI and low-level threading and vectorization layers cannot be easily partitioned for incremental changes. Even so, Feathers' basic strategy can guide part of the approach. In addition to Feathers' strategies, we need to use the same basic approach that succeeded when moving from vector to MPP codes. We need to first construct a new framework that includes only a minimal representative subset of the application's functionality. Then we construct the new framework to include the MPI (SPMD) and threading/vectorization layers of the old application, and a new task control layer in between the two. Proper design and implementation of these new frameworks is essential, and will impact scientific developer productivity and software sustainability. Adequate investment in R&D of best practices for scientific software is essential, and should be on an equal footing with R&D in other Office of Science research areas.

| Problem:                                             | Large sparse linear systems on von Neumann (vN) + accelerators/                | Score |  |  |  |  |  |  |  |

|------------------------------------------------------|--------------------------------------------------------------------------------|-------|--|--|--|--|--|--|--|

| interconnect/memory-centric. (Non von-Neumann notes) |                                                                                |       |  |  |  |  |  |  |  |

| Potential                                            | al Opportunities for R&D are numerous for all vN+accel, interconnect           |       |  |  |  |  |  |  |  |

|                                                      | and memory centric. (Non-vN options are possible, but appear to have           |       |  |  |  |  |  |  |  |

|                                                      | lower potential.)                                                              |       |  |  |  |  |  |  |  |

| Readiness                                            | adiness Current algorithms, with adaptations that are underway already, are    |       |  |  |  |  |  |  |  |

|                                                      | suitable for vN, interconnect and memory centric. (Fundamentally new           |       |  |  |  |  |  |  |  |

|                                                      | approaches are needed for non-vN.)                                             |       |  |  |  |  |  |  |  |

| Novelty                                              | Novelty Many known approaches that can be explored first. (There are potential |       |  |  |  |  |  |  |  |

|                                                      | algorithms for non-vN architectures. Solution of real valued systems can       |       |  |  |  |  |  |  |  |

|                                                      | be recast in the complex field for use with at least one known quantum         |       |  |  |  |  |  |  |  |

|                                                      | algorithm. ML-based approaches could be a suitable replacement for a           |       |  |  |  |  |  |  |  |

|                                                      | linear solver, at least to a coarse level approximation.)                      |       |  |  |  |  |  |  |  |

| Demand                                               | Linear solvers remain an important enabling capability for many scien-         | High  |  |  |  |  |  |  |  |

|                                                      | tific problems. On vN, interconnect and memory centric, funding for            |       |  |  |  |  |  |  |  |

|                                                      | new algorithms (which will typically be incremental) is important.             |       |  |  |  |  |  |  |  |

| Feasible                                             | Adaptations to all vN technologies are feasible with adequate resourcing.      | High  |  |  |  |  |  |  |  |

| Total                                                | Overall possibility that this is a high priority research direction.           | High  |  |  |  |  |  |  |  |

| Rating                                               |                                                                                |       |  |  |  |  |  |  |  |

Table 3.1: This table shows a simple illustration using sparse linear solvers as the target problem. For all von Neumann technologies, this is a good target problem. For non-von Neumann architectures, linear solvers do not have a clear mapping. In fact, alternative algorithms are most likely required, or the need to solve a linear system may be bypassed completely.

Despite some promise from initial efforts to introduce tasking, there are many research questions that must be addressed. Examples include what new mathematical formulations expose better computation intensity, how we can realize the potential of asynchronous execution in the presence of deep memory hierarchies that further penalize remote data accesses, how to effectively schedule fine grain dynamic work loads and how to write software that is easily adapted to a variety of heterogeneous processors. Furthermore, the disruptive change that this effort requires (similar to the vector-to-MPP transition in the 1990s) will be experienced across the entire DOE application portfolio. Over time, asynchronous tasking (for computation and data movement tasks) may become a replacement for message passing. A task-based model can provide a more expressive and flexible environment for parallel execution, especially for applications that have rapidly changing dynamic workloads.

### Chapter 4

# Future HPC Technologies: Opportunities and Challenges

In this chapter, we provide a summary of six major technologies (Chapters 4.1–4.6) that the subcommittee felt were most representative of the trends expected in future HPC systems, based on our current knowledge. While there are some natural omissions in this list (e.g., application-specific computers like Anton 2 [9], or computing with carbon nanotube transistors [10]), our belief is that the general findings and recommendations that were derived from studying these six technologies will apply to other future HPC technologies as well.

#### 4.1 Reconfigurable Logic

Application-specific acceleration hardware mapped onto Field Programmable Gate Arrays (FPGAs) offers a low-power, high performance option for exascale and post-exascale computing. Though the primary use of these devices was general purpose glue logic between ASICs, reconfigurable computing with FPGAs has been pursued for almost three decades [11], [12]. Over this period of time, FPGA architectures have evolved to complex systems on chip, including embedded processors, on-chip reconfigurable memory, network interfaces, DSP arithmetic blocks, and millions of system gates to hold arbitrary application-specific logic. For some application kernels, FPGAs can offer two orders of magnitude performance improvement over general purpose processors.

Research into reconfigurable computing was supported by the DARPA Adaptive Computing Systems program, which led to the design of coarse grained reconfigurable architectures such as PipeRench [13] from CMU, RAW [14] from MIT, and MorphoSys [15] from UC Irvine. Coarse grained architectures have primarily 8-16 bit data paths and function units in contrast to fine grained FPGAs with bit level resources. RAW was commercialized as the Tilera chip. Other commercial coarse grained reconfigurable architectures that have come and gone included MathStar [16] and Ambric [17]. The Tensor Processing Unit [18] from Google is a recent example of a coarse grained reconfigurable architecture specialized for neural network processing. While general purpose coarse grained architectures have not been stable in the marketplace, FPGAs remain highly successful commercial offerings with architectures suitable for a wide range of applications, including, for some large FPGAs, high performance computing.

Despite successful demonstration of many applications on FPGAs, interest in reconfigurable computing for HPC declined in the last decade with the advent of GPGPUs, which were capable of many factors of performance improvement over CPU at a fraction of the cost of high end FPGAs, and considerably easier application development cycle [19]. Recently however, the drivers of im-

#### Future High Performance Computing Capabilities

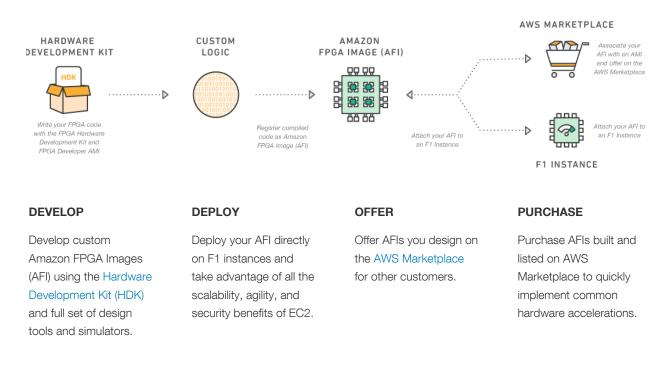

Figure 4.1: Growing an ecosystem for Amazon EC2 F1 FPGA instances (image source: https://aws.amazon.com/ec2/instance-types/f1)

proved performance per watt and better memory bandwidth utilization has resulted in a renewed interest in reconfigurable computing elements in exascale and post-exascale architectures.

Applications exploiting FPGAs were initially in bioinformatics (sequence alignment such as Smith Waterman or Needleman-Wunsch), signal processing, image processing, and network packet processing [20]. Of these, signal and image processing continue, especially in deployed platforms, and network packet processing has grown. The latter has been adopted in the finance sector [21] to enable microsecond turnaround by processing the packet payload on the network interface without having to make a round trip through the CPU. Database acceleration, data analytics for search engine applications and genomics have also been pursued, often in the context of an appliance. In scientific computing, recent algorithmic studies investigating the impact of reduced precision arithmetic on numerical stability are particularly relevant to reconfigurable logic that can support custom floating point formats [22].

The slow adoption of FPGAs for general purpose application acceleration has been principally due to the difficulty of mapping algorithms to hardware. For maximum performance, key kernels are written in Hardware Description Language (HDL), which requires hardware design expertise and has a much longer development cycle than software. High Level Synthesis (HLS) of C, C++, or OpenCL [23] continues to improve in quality of generated hardware and synthesizable subset of the language. However, performance gain is more comparable to GPU when HLS is employed. Additionally, the compile cycle (synthesis, map, place, and route) can take hours to days for large FPGAs and complex designs.

Factors that improve the prospects for reconfigurable computing with FPGAs in the exascale to post-exascale timeframe include

• increased urgency to reduce power while concurrently increasing compute capability

- improvements in design tools and access to design tools through the Amazon "free" design tool model (see below)

- increases in availability of open source hardware Intellectual Property (IP) libraries

- cloud-based application kernels and libraries from third party sources

- integration of data analysis with simulation

- workflows that can exploit in-transit data processing

**Technology Readiness Timeframe:** FPGAs are available today and with the Intel acquisition of Altera, it is feasible to have close integration of CPU with reconfigurable logic in 2-5 years. Early adoption in the data analysis and in-transit processing areas are most promising: for example, using reconfigurable logic to compress, clean, filter data streams generated by instruments [24].

Recently, FPGAs have become available in cloud computing servers, as illustrated by Amazon's F1 FPGA option for compute nodes (Figure 4.1). In the Amazon business model, application developers can create FPGA applications for the F1 in the Amazon cloud. Developers can offer those applications for customers to use. Customers pay for each use of the F1 configured to run the application in the same way they pay for any other cloud resource. This model enables more people to create FPGA applications since the cost of the CAD tools, FPGA board, and associated software are provided by Amazon. This model may ease the considerable burden of developing the reconfigurable computing hardware blocks for many commercial use cases, and may eventually lead to creation of an ecosystem that would support HPC needs.

#### 4.2 Memory-Centric Processing

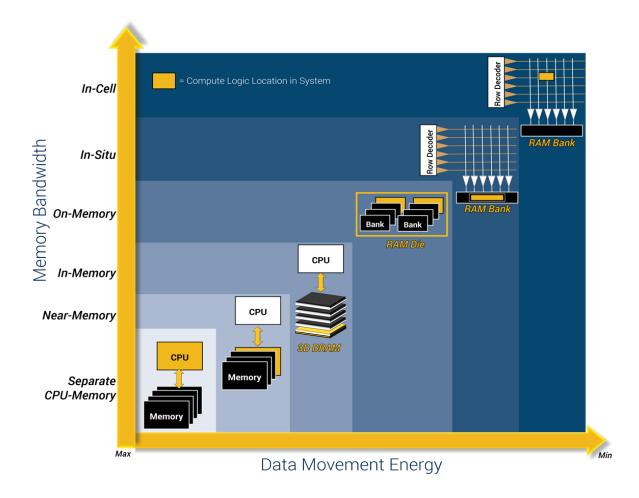

Memory-centric processing is a technique that places processing closer to memory than a conventional core. This typically means that the logic is outside the normal cache hierarchy, including typically outside the coherency mechanism for multi core. As shown in Figure 4.2, there is a definite taxonomy for memory-centric processing, which includes:

- In Cell: within the bit cell storing the data.

- At the Sense Amps: at the bottom of the block of memory cells, at the first point where the data is converted to a digital level, and where it has access to literally hundreds to thousands of bits from a complete "row"

- In-Situ: a bit further down the digital chain but still within a memory bank, typically just after a "column" multiplexer that is driven from the output of the sense amps.

- **On Memory**: on the memory die itself, typically with access to all the independent memory banks on the die.

- In Memory: On a die between a memory, or stack of memory die, and the processor.

- Near memory: near the memory controller that may be on the memory die, but typically on a processor die.

Table 4.1 illustrates several performance characteristics for these different levels of memorycentric processing. The columns are as follows:

|               | Bits Reachable | Bits per Access | Accesses per Sec (M/s) | Bandwidth (GB/s) | Movement on Chip | Functionality                      | ECC Possible |

|---------------|----------------|-----------------|------------------------|------------------|------------------|------------------------------------|--------------|

| In-Cell       | 1              | 1               | 50                     | 0.006            | 0                | Bit-level SIMD                     | No           |

| At Sense Amps | 1Mb            | 2Kb             | 50                     | 12+              | Down Column      | SIMD + Full core (Up<br>to Vector) | Yes          |

| In-Situ       | 1Gb            | 2Kb             | 50                     | 12+              | Down Column      | SIMD + Full core (Up<br>to Vector) | Yes          |

| On-Memory     | 8Gb            | 64b             | 400                    | 3.2              | Down Bank        | SIMD + Full core (Up<br>to Vector) | Yes          |

| In-Memory     | 4-8GB          | 1Kb             | 800                    | 100              | Across Chip      | Full Core                          | Yes          |

| Near-Memory   | 64+GB          | 64B             | 400                    | 3.2              | Across Chip      | Full Core                          | Yes          |

Table 4.1: Performance characteristics for different levels of memory-centric processing.

- Bits Reachable: the number of different bits that might be accessible by a core at the specified location generating an address. For example, for "In-Situ" a core would have access to all the data in the memory block, whereas for "On Memory" it may have access to any of the memory on the die.

- Bits per Access: On each access, how many bits are possibly returned to the core. For example, for "In-Situ" it may be the width of a memory bank row.

- Accesses per Sec (M/s): From a core in the specified position, how many different memory accesses could be made per second. For example, a 3200 MT/s DDR4 DIMM with a burst depth of 8 can make up to 400M accesses/s.

- Bandwidth: The product of the above terms, bits per access and access rate.

- Movement on Chip: How far across a die must data be moved to get to either the processing core or the off-chip interface that leads to the core. This is a significant energy event.

- Chip Crossings per Access: How many times must a chip edge be crossed. This is a very significant energy event.

- Functionality: What kind of processing is reasonable.

- ECC Possible?: Is it feasible to include ECC both the extra bits and the logic.

The rationale for doing this comes from the increasing need to speed up problems where memory bandwidth dominate, and where there is a lot of memory against which perhaps specialized operations are to be performed. The benefits include reduced latency, reduced energy of transport, ability to make atomic operations go faster, and high levels of concurrency in systems with lots of memory and memory channels. Architecturally, the key issues are how to maintain some level of coherency with copies of the same data further down the cache hierarchy, how to spawn such

Figure 4.2: Different levels of memory-centric processing

remote computations, how to maintain a global address space, how to recognize completion of such operations, and how to handle cases where data from several separated memories need to be combined.

**Technology Readiness Timeframe:** Looking forward, while examples exist of all these techniques today, the latter (Near Memory) is perhaps of most interest in the applicability to 3D stacks, where the bottom of the stack has logic and network routing, and this is at worst a few years away there is no technological challenge. Also DARPA's "chiplet" program may very well develop processors that can be combined with a variety of memory technologies, as will possibly SRC's recently awarded JUMP programs. Candidates for "killer apps" include memorycentric streaming operations such as encryption/decryption, search, big data, big graphs, and possibly deep learning.

#### 4.3 Silicon Photonics

Among the technologies emerging toward creating a fundamentally energy efficient interconnect, photonics is perhaps the most promising to enable a transition to a new generation of scaled extreme performance computing systems [25]. Optical technologies can directly impact the critical commu-

nications challenges within computing systems through their remarkable capabilities to generate, transmit, and receive ultra-high bandwidth densities with fundamentally superior power efficiencies and with inherent immunity to noise and degradation. Unlike prior generations of photonic technologies, recent breakthroughs in silicon photonics offer the possibility of creating highly-integrated platforms with dimensions and fabrication processes compatible with electronic logic and memory devices. During the past decade, a series of major breakthroughs in silicon photonic devices has demonstrated that all the components that are necessary to build chip-scale photonic interconnect components (e.g. modulators, filters, switches, detectors) can be fabricated using common CMOS processes.

#### 4.3.1 Current Photonic Interconnect Technologies

Most optical links in todays supercomputers are based on multi-mode optical fibers and Vertical Cavity Surface Emitting Lasers (VCSELs). They are also generally built around a one channel per fiber format. Signals received from the electrical side are directly used to drive the laser diode, without format conversion or adaptation of any kind. Based on recommendations issued by standardization bodies such as IEEE, transceivers receive electrical signals at 10, 14, 28 Gb/s on one to ten lanes, each being coupled into its separate fiber. Transceivers with electrical signals at 56 Gb/s (QSFP56 format) will arrive soon in the market. Standards for electrical signaling at 112 Gb/s are in preparation. Traditional non-return-to- zero (NRZ) signaling will be kept for 56G but most likely PAM4 signaling will be adopted for higher speeds. Directly modulated VCSELs have been shown capable of supporting extreme bitrates provided that the adequate driving circuitry realizing pre-emphasis is provisioned alongside [26]. The power consumption of these circuits, however, may become discouraging. Products with 50 Gb/s or more per lane are only about to emerge, but VCSEL based systems have been scaled beyond the 50 Gb/s already, by means of fiber parallel systems. Multi fiber array connectors (MPO) with up to 24 fibers have been standardized (TIA 604-5-D) and standards with 72 fibers are in preparation. Such fiber ribbons and multi fiber connectors are, for instance, used in commercial products as Ciscos CPAK 100GBASE-SR10 module. The CDFP standard is based on cables made of 32 fibers. Having multiple fibers in parallel has obviously an impact on cable management and cable cost. In addition, connectors involving many fibers are susceptible to show a higher loss. For this reason, VCSEL based multi-wavelength links (coarse WDM) have been proposed. The acronym SWDM, standing for Shortwave Wavelength Division Multiplexing, has been recently introduced to distinguish this technology. To realize the multiplexing and demultiplexing operations, thin-film filters based solutions are among the most mature. Each thin film transmits a wavelength and reflects the others, at low loss in both cases. Such filters are cascaded to progressively isolate all wavelengths. Solutions to efficiently couple signals emitted by an array of VCSELs into optical fibers have also been investigated. Shortreach VCSEL based transceivers are expected to scale to 1 Tb/s bandwidth by means of highly fiber-parallel cables and/or WDM, in conjunction with high-speed signaling at or beyond 50 Gb/s. VCSELs have the important property to authorize testing at the wafer level, whereas other laser sources must generally be tested after dicing. They also show an emission aperture about three times larger, which greatly facilitates packaging. Altogether, these advantages allow VCSEL based links to show cost figures of a few dollars per Gb/s. This metric will be further scaled down by means of higher signaling speeds, increased wavelength and/or fiber parallelism, and as a result of further simplified packages and test procedures. Increase in manufacturing volumes should also drive the cost down.

Figure 4.3: Current photonic interconnect technologies

#### 4.3.2 Emerging Silicon Photonics Interconnect Technologies

Silicon photonics (SiP) emerged in the last decade as a promising optical interconnect technology. SiP takes advantage of the high index contrast between silicon (3.476 at 1550 nm) and silica (1.444 at 1550 nm) to enable micro-meter scale optical guiding structures such as add-drop filters and switches. For modulation, free-carrier dispersion effect is the only mechanism in silicon fast enough to enable purely silicon-based high-speed electro-optic modulation (10 Gb/s and beyond). Modulators are controlled by placing a PN or PIN region with typical doping levels on the order of 1017 1018 cm3 around the modulating structure. Combined with the resonant nature of ring resonators, compact wavelength-selective electro-optic modulators with very small footprint can be realized in SiP platforms [27]. An array of such modulators can provide WDM transmission with aggregate rates in the excess of 100 Gb/s. Modulation can also be realized in silicon alone by means of MachZehnder Interferometers (MZI). MZIs are less sensitive to thermal fluctuation than ring resonators, but are not wavelength selective, obliging each wavelength to be independently modulated before being multiplexed. Another modulation approach consists of selectively growing SiGe waveguides on top of a silicon wafer to form an electro-absorption modulator.

Unlike VCSELs that are directly modulated, a silicon photonic platform relies on modulators that imprint the desired information on a continuous wave light generated by an external laser. Due to its intrinsic material properties, Silicon is an extremely poor light emitter. Light generation and emission thus relies on lasing of other material systems (e.g. IIIV semi- conductors). The promise of using already advanced CMOS infrastructure for mass production of SiP is therefore challenged by the complexity of on-chip optical power generation. Co-packaging of an external laser with the SiP chip or flip-chip bonding are the solutions that have been already investigated. So far, however, no cost-efficient packaging solution has emerged. Packaging challenges must also be addressed with respect to the coupling of light from SiP chip to the single-mode fibers. Although single-mode fibers are cheaper than multi-mode fibers, their connection to the SiP chip via grating couplers or edge-couplers typically require accurate alignment to avoid high optical loss. This in turn adds an additional level of complexity to the overall packaging of SiP. This situation, in comparison, is much more relaxed for the connection of VCSELs to multi-mode fibers thanks to their considerably larger core diameter and to the wide aperture of VCSELs. Silicon photonics systems based on single-mode fibers support a much wider use of wavelength multiplexing than their VCSEL-based counterparts. This potentially permits to amortize coupling-related packaging cost over larger link data-rates. The cost of the external optical power source can similarly be mitigated if a single laser capable of simultaneously emitting multiple wavelengths (comb laser) is used.

WDM operation can provide unprecedented interconnect bandwidths that fall well within the requirements of supercomputers in the near future. This concept was demonstrated by using a single quantum dot comb laser and an array of SiP ring modulators with 10 Gb/s per laser line. Based on this capability recent work on SiP-based DWDM interconnects showed the possibility of 1.56 Tb/s bandwidth at 25 Gb/s signaling rate and overall 7.5 pJ/bit consumption (assuming full link utilization) [28]. More recently, updated work showed a maximum aggregation of 2.1 Tb/s at 45 Gb/s per channel.

There are strong motivations to co-integrate the optical transceivers with compute modules (CMP or GPU), as well as with memory packages. A single package allows cost reduction for OEM vendors, reduces the wiring complexity on boards, results in higher component density, and most importantly can reduce signal degradation between data source and optical transceiver. If transceivers and data sources are placed in close proximity, their communication can be simplified and greater power and area saving can be achieved. In 2012 Altera together with Avago demonstrated an FPGA VCSEL transceiver assembly using a package on pack- age (PoP) approach. The optical aggregate bitrate of the FPGA assembly reached 120 Gb/s. Recent packaging trends are aiming at a closer integration of transceivers and ICs within the same package. System in package products integrate several chips within one package by coupling them using a common interposer. The interposer will incorporate dc and transmission lines to interconnect all dice within the package. In the easiest case the dice are coupled to the interposer using wire bonds. Flip-chip assemblies are a prominent technique to connect high performance chips. It allows for very low parasitic connections between a data source and a transceiver in the same package. It becomes even more interesting if the underlying interposer is a silicon photonic chip, integrating modulators and receivers that are steered by the stacked chips.

A silicon photonic interposer enables optical networks in-package either for high bitrate communication of chips within the same package or at the same speed with peripherals as the package boundary is of no importance for optical signals. The highest level of integration is reached when the data source integrates optics on the same die, so called monolithic solutions. Monolithically integrated chips have the smallest parasitic loadings possible. Therefore, they show very high energy efficiencies. However, CMOS processes are not optimal for silicon photonic structures. In addition, optical structures cannot be arbitrarily reduced in size and a single modulator will stay several micro meters big. Hence, monolithic solutions are very costly if integrated with modern deep sub-micrometer CMOS processes. From a geometrical perspective it is a challenge to integrate a sufficient number of pins and transceivers into each die or package to carry all the data in and out. Both directly modulated VCSELs as well as silicon photonic transceivers can emit and receive light into and from fibers perpendicularly oriented to the chip plane. If a chip does not need to carry the data to the optical transceiver by a 2D interposer but instead can emit and receive on the top surface of the die or die stack itself, very high bitrate densities can be achieved, independent from the overall packaging approach.

To a large extent, but not completely, independent of how the electrical chip is interfaced with the optical transceivers is the connection of fibers or optical connectors to the optical transceivers. VCSELs can be directly coupled to multimode fibers. In this case the fiber is always perpendicular to the VCSEL and therefore to the package it is assembled upon. The advantage of multimode fibers is their large aperture which leads to high fabrication tolerance and passive alignment structures. If VCSELs are used for WDM to increase the bitrate per fiber, micro optical packaging needs to be employed. Micro optical packaging requires very high precision assemblies that are expensive

#### Future High Performance Computing Capabilities

to process. Because the structures on silicon photonic chips are much smaller, coupling light from an on-chip waveguide into a fiber is a challenge that leads to many solutions. Good coupling can only be achieved if the light mode (the phase and intensity distribution) is matched on chip to the mode inside common fibers.