# Top Ten Exascale <u>Research Challeng</u>es

DOE ASCAC Subcommittee Report February 10, 2014

Sponsored by the U.S. Department of Energy, Office of Science, Office of Advanced Scientific Computing Research

#### ASCAC Subcommittee for the Top Ten Exascale Research Challenges

#### Subcommittee Chair

Robert Lucas (University of Southern California, Information Sciences Institute)

#### Subcommittee Members

James Ang (Sandia National Laboratories) Keren Bergman (Columbia University) Shekhar Borkar (Intel) William Carlson (Institute for Defense Analyses) Laura Carrington (UC, San Diego) George Chiu (IBM) Robert Colwell (DARPA) William Dally (NVIDIA) Jack Dongarra (U. Tennessee) Al Geist (ORNL) Gary Grider (LANL) Rud Haring (IBM) Jeffrey Hittinger (LLNL) Adolfy Hoisie (PNLL) Dean Klein (Micron) Peter Kogge (U. Notre Dame) Richard Lethin (Reservoir Labs) Vivek Sarkar (Rice U.) Robert Schreiber (Hewlett Packard) John Shalf (LBNL) Thomas Sterling (Indiana U.) Rick Stevens (ANL)

#### Acknowledgements

The ASCAC Subcommittee for the Top Ten Exascale Research Challenges would like to thank the following for their contributions to this report.

Jon Bashor (LBNL) Ron Brightwell (Sandia National Laboratories) Paul Coteus (IBM) Erik Debenedictus (Sandia National Laboratories) Paul Franzon (North Carolina State University) Scott Hemmert (Sandia National Laboratories) Jon Hiller (Science and Technology Associates) K.H. Kim (IBM) Harper Langston (Reservior Labs) James Laros III (Sandia National Laboratories) Sven Leyffer (ANL) Richard Murphy (Micron) Rob Ross (ANL) Clayton Webster (ORNL) Stefan Wild (ANL)

#### Cover Image

Cover image was produced by a multidisciplinary team that includes LANL researcher Hussein Aluie of the Computational Physics and Methods group and the Center for Nonlinear Studies reports an alternative explanation, involving turbulence, for the fast magnetic reconnection.

### Contents

| 1 | Exe        | cutive           | Summary                                                                      | 1        |

|---|------------|------------------|------------------------------------------------------------------------------|----------|

|   | 1.1        | The T            | op Ten Exascale System Research Challenges                                   | 1        |

|   | 1.2        |                  |                                                                              | 2        |

|   |            | 1.2.1            |                                                                              | 2        |

|   |            | 1.2.2            |                                                                              | 2        |

|   |            | 1.2.3            | The U.S. has the technical foundation to create exascale systems.            | 3        |

|   |            | 1.2.4            | •                                                                            | 3        |

|   |            | 1.2.5            | The U.S. government's continuous leadership and investment are required to   |          |

|   |            |                  |                                                                              | 3        |

|   | 1.3        | Summ             |                                                                              | 3        |

|   |            | 1.3.1            |                                                                              | 3        |

|   |            | 1.3.2            | DOE should invest in the U.S. industrial base to catalyze the foundation for |          |

|   |            |                  |                                                                              | 3        |

|   |            | 1.3.3            | DOE should invest in exascale mathematics and system software responsive     |          |

|   |            |                  |                                                                              | 3        |

|   |            | 1.3.4            | DOE should create an Open Exascale System Design Framework to enable         |          |

|   |            | -                |                                                                              | 4        |

|   |            |                  |                                                                              |          |

| 2 | Intr       | oducti           | on                                                                           | <b>5</b> |

|   | 2.1        | Challe           | nges                                                                         | 5        |

|   | 2.2        | Integra          | ating the Results                                                            | 7        |

|   | 2.3        | Overv            | ew                                                                           | 8        |

|   |            |                  |                                                                              |          |

| 3 |            |                  |                                                                              | 9        |

|   | 3.1        |                  | $\sim$ 0                                                                     | 9        |

|   | 3.2        |                  | Threshold Voltage (NTV)     1                                                |          |

|   | 3.3        | Energ            | y Efficient Architecture                                                     |          |

|   | 3.4        | Energ            | y Efficient Interconnects  1                                                 |          |

|   | 3.5        |                  | ry and Register Files                                                        |          |

|   | 3.6        |                  | nt On-Chip Power Delivery and Management                                     | 3        |

|   | 3.7        | System           | n-Scale Power Management                                                     | 4        |

|   | 3.8        | Impac            | t                                                                            | 6        |

|   | <b>.</b> . |                  |                                                                              | _        |

| 4 |            |                  | ect Technology 1                                                             |          |

|   | 4.1        |                  | Movement Energy and Bandwidth Challenges                                     |          |

|   | 4.2        |                  | e Interconnect Fabric                                                        |          |

|   | 4.3        |                  | hip Network Integration                                                      |          |

|   | 4.4        |                  | nics                                                                         |          |

|   | 4.5        | Impac            | t 2                                                                          | 0        |

| 5 | Мо         | mont 7           | Cechnology 2                                                                 | 1        |

| 9 |            | •                |                                                                              |          |

|   | 5.1        |                  | 8                                                                            |          |

|   |            | $5.1.1 \\ 5.1.2$ | Energy       2         Scaling       2                                       |          |

|   |            | 5.1.2<br>5.1.3   | Scaling                                                                      |          |

|   |            |                  |                                                                              |          |

|   |            | 5.1.4            | Systems Tradeoffs and Integration:                                           | 4        |

|    | 5.2        | Research Directions                                                                                                                                        |

|----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 5.3        | Impact                                                                                                                                                     |

| 6  | Sca        | lable System Software 26                                                                                                                                   |

|    | 6.1        | Research Directions                                                                                                                                        |

|    | 6.2        | Lightweight OS                                                                                                                                             |

|    | 6.3        | Runtime Systems                                                                                                                                            |

|    | 6.4        | Introspection                                                                                                                                              |

|    | 6.5        | Energy Management                                                                                                                                          |

|    | 0.5<br>6.6 | Impact                                                                                                                                                     |

|    | 0.0        | Impact                                                                                                                                                     |

| 7  | Pro        | gramming Systems 32                                                                                                                                        |

|    | 7.1        | Programming Models and Notations                                                                                                                           |

|    | 7.2        | Compilers                                                                                                                                                  |

|    | 7.3        | Main Exascale Challenges for Compilers R&D Focus                                                                                                           |

|    | 7.4        | More Knobs for Programmers                                                                                                                                 |

|    | 7.5        | Compiler Research Directions                                                                                                                               |

|    | 7.6        | Development Model                                                                                                                                          |

|    | 7.7        | Impact                                                                                                                                                     |

|    |            |                                                                                                                                                            |

| 8  |            | a Management 38                                                                                                                                            |

|    | 8.1        | Exascale Data Management Challenges                                                                                                                        |

|    |            | 8.1.1 Challenges Common to both Offensive and Defensive I/O                                                                                                |

|    |            | 8.1.2 Challenges Specific to Defensive I/O                                                                                                                 |

|    |            | 8.1.3 Challenges Specific to Offensive I/O 39                                                                                                              |

|    | 8.2        | Research Directions                                                                                                                                        |

|    | 8.3        | Impact                                                                                                                                                     |

| 9  | Exa        | scale Algorithms 43                                                                                                                                        |

|    | 9.1        | Multicore-Friendly and Multicore-Aware Algorithms                                                                                                          |

|    | 9.2        | Communication Avoiding Algorithms                                                                                                                          |

|    | 9.3        | Synchronization Reduction                                                                                                                                  |

|    | 9.4        | Multi-Physics Algorithms                                                                                                                                   |

|    | 9.5        | Multi-Scale Algorithms                                                                                                                                     |

|    | 9.6        | Adaptive Response to Load Imbalance                                                                                                                        |

|    | 9.7        | Scheduling and Memory Management for Heterogeneity and Scale                                                                                               |

|    | 9.8        | Energy-Efficient Algorithms                                                                                                                                |

|    | 9.9        | Automatic Adaptation of Algorithms                                                                                                                         |

|    | 9.10       |                                                                                                                                                            |

|    |            |                                                                                                                                                            |

|    | 9.11       | Impact                                                                                                                                                     |

| 10 | _          | orithms for Discovery, Design, and Decision 48                                                                                                             |

|    | 10.1       | Research Directions                                                                                                                                        |

|    |            | 10.1.1 Uncertainty Quantification                                                                                                                          |

|    |            | 10.1.2 Optimization $\ldots \ldots \ldots$ |

|    | 10.2       | Impact                                                                                                                                                     |

| 11 Resilience and Correctness                                                                                                          | <b>52</b> |

|----------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 11.1 Hardware Support and Performance Modeling                                                                                         | 53        |

| 11.2 Programming Models and Environment                                                                                                | 53        |

| 11.3 Algorithmic-Based Fault Tolerance                                                                                                 | 53        |

| 11.4 Correctness                                                                                                                       | 54        |

| 11.5 Impact                                                                                                                            | 54        |

| 12 Scientific Productivity                                                                                                             | 55        |

| 12.1 Research Directions                                                                                                               | 55        |

| 12.2 Impact                                                                                                                            | 57        |

| 13 Co-Design and Integration Framework                                                                                                 | 58        |

| 13.1 Execution Model                                                                                                                   | 58        |

| 13.2 Architecture                                                                                                                      | 59        |

| 13.3 Performance Metrics                                                                                                               | 60        |

| 13.4 Co-Design Integration Framework                                                                                                   | 62        |

| 13.5 Modeling and Simulation of Exascale Systems and Applications                                                                      | 64        |

| 14 Findings and Recommendations                                                                                                        | 66        |

| 14.1 Findings                                                                                                                          | 66        |

| 14.1.1 Exascale computing is critical for executing the DOE mission                                                                    | 66        |

| 14.1.2 U.S. national leadership is at risk. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                             | 66        |

| 14.1.3 The U.S. has the technical foundation to create exascale systems                                                                | 66        |

| 14.1.4 An evolutionary approach to achieving exscale will not be adequate                                                              | 66        |

| 14.1.5 The U.S. government's continuous leadership and investment are required to                                                      | ~         |

| create exascale systems.                                                                                                               | 67        |

| 14.2 Recommendations                                                                                                                   | 67        |

| 14.2.1 DOE should initiate a program of continuous advancement in HPC                                                                  | 67        |

| 14.2.2 DOE should invest in its industrial base to catalyze the foundation for exas-                                                   | 07        |

| cale systems.                                                                                                                          | 67        |

| 14.2.3 DOE should invest in exascale mathematics and system software responsive to DOE missions and other U.S. government requirements | 68        |

| 14.2.4 DOE should create an Open Exascale System Design Framework to enable                                                            | 00        |

|                                                                                                                                        | 69        |

| 15 Bibliography                                                                                                                        | 70        |

|                                                                                                                                        |           |

| References                                                                                                                             | 78        |

| A Charge Letter                                                                                                                        | 79        |

### List of Figures

| 1  | Energy efficiency and variability in NTV operation.                                    | 11 |

|----|----------------------------------------------------------------------------------------|----|

| 2  | Compute and interconnect energy.                                                       | 12 |

| 3  | Integrated voltage regulator.                                                          | 13 |

| 4  | Clock and power gating.                                                                | 14 |

| 5  | Bandwidth vs system distance                                                           | 17 |

| 6  | Energy vs system distance                                                              | 17 |

| 7  | Memory capacity (Bytes) per gigaflop/s, courtesy of Peter Kogge.                       | 22 |

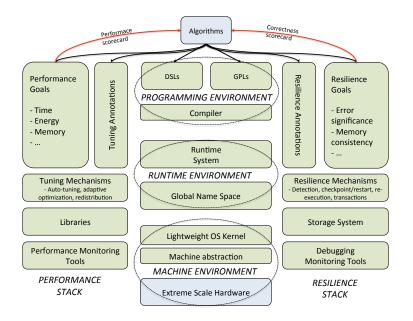

| 8  | Notional programming system structure with programming, runtime, and machine           |    |

|    | environments, and performance and resilience "stacks."                                 | 32 |

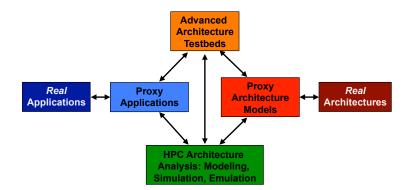

| 9  | Simplified versions of the target hardware and target application enable rapid pro-    |    |

|    | totyping and assessment of future hardware/software interactions. Accurate proxy       |    |

|    | models for the hardware and software make the size and complexity of the model-        |    |

|    | ing problem tractable. Accurate predictive modeling and simulation tools for future    |    |

|    | hardware are essential for enabling crucial design decisions for very expensive system |    |

|    | designs before they are built (or written in the case of software).                    | 63 |

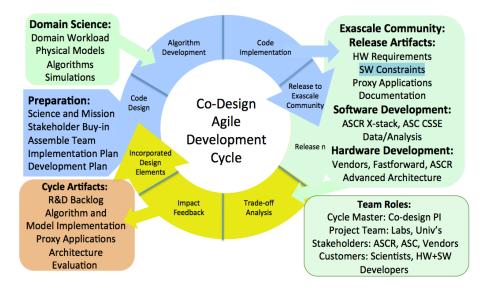

| 10 | Typical co-design process for the design of co-tuned hardware and software systems.    | 64 |

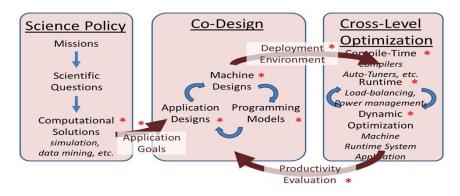

| 11 | Notional HPC workflow. The * represent domains for modeling and simulation             | 65 |

#### The Top Ten Exascale Research Challenges

#### **1** Executive Summary

Exascale computing systems are essential for the scientific fields that will transform the 21stcentury global economy, including energy, biotechnology, nanotechnology, and materials science. Progress in these fields is predicated on the ability to perform advanced scientific and engineering simulations, and analyze the deluge of data. The Department of Energy's 2011 strategic plan and 2012 addendum calls out a Priority Goal: *Lead Computational Sciences and High-Performance Computing* and a Targeted Outcome: *Continue to develop and deploy high-performance computing* hardware and software systems through exascale platforms.

On July 29, 2013, ASCAC was charged by Patricia Dehmer, the Acting Director of the Office of Science, to assemble a subcommittee. This subcommittee was directed to return "a list of no more than ten technical approaches (hardware and software) that will enable the development of a system that achieves the Department's exascale goals, particularly the usability goals for the Department's mission-critical applications, as articulated in the attached presentation. That is, given the known technical barriers that could prevent the development of a computer that achieves the Department's exascale goals, what are credible technical approaches for overcoming these barriers? The subcommittee's report should provide compelling justifications for including each item in the list and describe the expected impact on overall system performance." This report, in response to DOE's charge, details key technological barriers to achieving productive exascale platforms, along with recommended approaches to overcome these barriers.

Numerous reports over the past five years have documented the technical challenges and the non-viability of simply scaling existing computer designs to reach exascale. The technical challenges revolve around energy consumption, memory performance, resilience, extreme concurrency, and big data. Drawing from these reports and more recent experience, this ASCAC subcommittee has identified the top ten computing technology advancements that are critical to making a productive, economically viable, exascale system. Note, the challenges are not rank-ordered by importance, but rather grouped by the subcommittee into related categories.

#### 1.1 The Top Ten Exascale System Research Challenges

- 1. Energy efficiency: Creating more energy-efficient circuit, power, and cooling technologies.

- 2. Interconnect technology: Increasing the performance and energy efficiency of data movement.

- 3. Memory Technology: Integrating advanced memory technologies to improve both capacity and bandwidth.

- 4. Scalable System Software: Developing scalable system software that is power- and resilienceaware.

- 5. Programming systems: Inventing new programming environments that express massive parallelism, data locality, and resilience

- 6. Data management: Creating data management software that can handle the volume, velocity and diversity of data that is anticipated.

- 7. Exascale Algorithms: Reformulating science problems and redesigning, or reinventing, their solution algorithms for exascale systems.

- 8. Algorithms for discovery, design, and decision: Facilitating mathematical optimization and uncertainty quantification for exascale discovery, design, and decision making.

- 9. Resilience and correctness: Ensuring correct scientific computation in face of faults, reproducibility, and algorithm verification challenges.

- 10. Scientific productivity: Increasing the productivity of computational scientists with new software engineering tools and environments.

Innovative solutions to the challenges identified in these ten areas are on the critical path to delivering effective HPC systems for critical science and technology areas that underpin U.S. economic competitiveness for the 21st century. For example, advances in near-threshold-voltage circuit technology hold the promise of improving energy efficiency of systems by nearly an order of magnitude, but it will require a revolutionary change in programming environments and application design to tap into this opportunity. Without dramatic reformulation of hardware together with software, exascale systems are projected to consume 100s of megawatts, and few existing HPC applications will be able to scale beyond a tenth of an exaflop. Without the advances in programming models and productivity described in this report, it will not be feasible to redesign algorithms and application codes to provide efficient and correct answers. And without the tools to analyze the data from experiment and simulation, scientists will be overwhelmed by the data volume generated by next generation scientific instruments and advanced computing facilities. Each of the ten areas plays an essential role in enabling a practical and effective HPC technology for the next decade, which in turn impacts the DOE mission, and more broadly ensures U.S. leadership in these key science and technology fields. Unlike past systems, the next generation of supercomputers needs to be developed using co-design approaches where scientific problem requirements guide computer architecture and system software design. Doing so will require long-term partnerships among vendors, government agencies, and academia.

In the course of conducting this study, the subcommittee considered a number of related issues that add context to the top ten research challenges and the means to overcome them. To further assist the DOE in planning its future research directions, these issues are addressed in a series of findings and recommendations.

#### 1.2 Summary of Findings

#### 1.2.1 Exascale computing is critical for executing the DOE mission.

ASCAC reaffirms its findings from previous reports that leadership in high performance computing (HPC) is critical to achieving the DOE mission of ensuring U.S. leadership in science, engineering, and national security. In the last six years, this has been documented in many exascale reports from Office of Science programs, the National Nuclear Security Administration, and other U.S. government agencies.

#### 1.2.2 U.S. national leadership is at risk.

Without aggressive investment and technical innovation in HPC, the U.S. risks falling behind rapidly emerging international competitors, not all of whom are friendly to U.S. interests. This in turn threatens to undermine the nation's intellectual leadership in a broad range of science, its economic position, and its security.

#### **1.2.3** The U.S. has the technical foundation to create exascale systems.

The U.S. semiconductor and HPC systems industries are capable of developing the necessary technologies for an exascale computing capability by the early part of the next decade, based largely on evolving commercially driven component fabrication, systems integration, and software engineering capabilities. However, for a truly effective and productive exascale computing capability, the U.S. government will need to focus investments on the research, development, and integration of HPC technologies that will otherwise not be created solely by commercial drivers.

#### 1.2.4 An evolutionary approach to achieving exascale will not be adequate.

The dramatic improvements essential to achieving effective exascale computing will not be satisfied by incremental extensions to today's conventional practices. Commercial market drivers do not provide a viable general path to delivering necessary scalability, time and energy efficiency, and user productivity including performance portability to future generation exascale class computers.

## **1.2.5** The U.S. government's continuous leadership and investment are required to create exascale systems.

The U.S. computing industry is unlikely to develop effective exascale computer systems without U.S. government investment and focused mission goals. Innovation, sometimes of an incremental nature, and in other areas revolutionary, will be required under DOE direction to enable U.S. leadership in advanced HPC.

#### **1.3** Summary of Recommendations

#### 1.3.1 DOE should invest in a program of continuous advancement in HPC.

Exascale is only the next milepost in a half-century of continuous progress towards increasing capability in computational science. The U.S. government requires a stable, long-term investment strategy to ensure continuous U.S. leadership in HPC beyond today's petascale performance regime, extending to exascale and beyond. In the immediate future, much of that research investment should be focused on the top ten challenges identified within this report.

# **1.3.2** DOE should invest in the U.S. industrial base to catalyze the foundation for exascale systems.

DOE should invest in extending commercial semiconductor, communications, systems integration, and software technologies to prepare the U.S. industrial base for its role and contributions in future HPC scientific, engineering and national security missions. All of these exascale components must be developed by and be available from U.S. sources, otherwise the supply chain is vulnerable to interdiction by foreign powers, which in turn could threaten the nation's security.

### **1.3.3** DOE should invest in exascale mathematics and system software responsive to DOE missions and other U.S. government requirements.

The mathematical algorithms needed for many DOE missions are unique, and must be reinvented to function at exascale. As with today's Leadership-class systems, much of the software infrastructure of an exascale system will be unique to its scale and the missions for which DOE will deploy it. Therefore, DOE must invest in robust and scalable mathematical algorithms, operating systems, runtime systems, and tools for the management of the data that will be generated and/or processed.

## **1.3.4** DOE should create an Open Exascale System Design Framework to enable cooperative hardware and software advancement.

DOE's understanding of government mission drivers provides a critical foundation to coordinate requirements for and development of interoperable system components. Thus DOE should establish a co-design framework for collaboration and system integration of crosscutting component layers. Such a framework will serve as the conceptual scaffolding for the development of new programming language and hardware architecture, runtime software and operating system, application algorithms along with their data and workflows, and management policies for future exascale computing.

#### 2 Introduction

Scientific progress has been, and will continue to be, a notable source of American prosperity and leadership in world affairs. High performance computing (HPC), has a fundamental role to play in enabling scientific progress. The DOE mission elevates the importance of leadership in this space for national security and economic reasons. This spans a broad range of DOE missions, including new energy solutions, ecological sustainability, global climate change, next generation nuclear power plants, scientific discovery, and global security. This is reflected in the Department of Energy's 2011 strategic plan. The 2012 addendum calls out both a Priority Goal: *Lead Computational Sciences and High-Performance Computing*, and a Targeted Outcome: *Continue to develop and deploy high-performance computing hardware and software systems through exascale platforms*. Based on this fact alone, one would expect continued and substantial investment in HPC.

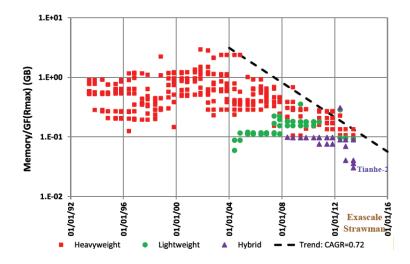

It is remarkable to observe that computing is becoming central to progress even for the most fundamental research in the sciences. Maintaining U.S. leadership in computational science requires the best tools. This includes a succession of computer resources with world-class capability as well as the data storage and analysis tools needed to effectively use the results. As is stated in the DOE Office of Science (DOE SC) strategic plan, "Each of the [scientific] goals, and progress in many other areas of science, depends critically on advances in computational modeling and simulation. Crucial problems that we can only hope to address computationally require us to deliver effective computing power orders-of-magnitude greater than we can deploy today." That implies exascale,  $10^{18}$  operations per second, the next major milestone in a process of exponential improvement that has continued for over half a century. For the purposes of this report, the definition of exascale is more than just a peak rate of sustained arithmetic operations, bytes of storage, or the familiar High Performance Linpack (HPL) [117] Rmax floating-point operations per second (Flop/s). Exascale is a relative term suggesting 1000-fold better capability than representative from the petascale, which started circa 2009. This definition encompasses 1000-fold improvements in the usable performance of systems at all scales relative to the 2009 baseline, not just the largest. As such, exascale suggests a practical delivered capability within the scope of achievable power, reliability, size, cost, programmability, and other constraints. Such a system cannot be produced today, and identifying research required to achieve this capability is the purpose of this report.

While DOE is able to maintain its position of leadership today, that position is threatened in the near future [93]. Underlying technology is changing dramatically now. The models of scaling that formed the basis of ever increasing computer power are ending [73, 113]. Dennard scaling [32] is over, and while Moore's Law [84] continues, its demise is in sight too. Therefore, the future of high performance computing (HPC) is unknown. This in turn threatens to compromise DOE's ability to perform the leadership aspect of its mission. This is not the first time this has happened. Circa 1990, CMOS device technology overtook TTL (Transistor Transistor Logic) and ECL (Emitter Coupled Logic). DOE led the way to a new stable point in HPC, communicating sequential processes (CSP) [60] integrated from commercial, off-the-shelf technology (COTS). DOE needs to do it again, as nobody else in U.S. is stepping up. The alternative is for the United States to cede leadership in HPC to Europe, Japan, and/or China

#### 2.1 Challenges

Given the importance of exascale computing to DOE, on July 29, 2013, ASCAC was charged by Patricia Dehmer, the Acting Director of the Office of Science, to assemble a subcommittee. This subcommittee was directed to return "a list of no more than ten technical approaches (hardware and software) that will enable the development of a system that achieves the Department's exascale goals, particularly the usability goals for the Department's mission-critical applications, as articulated in the attached letter. That is, given the known technical barriers that could prevent the development of a computer that achieves the Department's exascale goals, what are credible technical approaches for overcoming these barriers? The subcommittee's report should provide compelling justifications for including each item in the list and describe the expected impact on overall system performance."

This report, written in response to the charge, describes ten key technical areas that need substantial research and development in order create a productive, economically viable, broadly useful, exascale system, and enable DOE to perform its mission. The report also discusses the impact that advances in each of the ten areas will have on the exascale system's performance and its ability to solve the science problems critical to the nation. Numerous reports over the past five years have documented the technical challenges and the non-viability of existing computer designs to simply scale to exascale. The technical challenges revolve around energy consumption, memory performance, resilience, and extreme concurrency. These challenges are the drivers for the research that must be done.

To determine the top ten research and development areas, a group of 23 experts in high performance computing hardware and software was assembled. These experts were from industry, academia, and government-funded research laboratories. They met dozens of times, both in person and by telephone, analyzed the state of the technology upon which an exascale system will be developed, and came up with the following top ten challenges. The challenges are not rank-ordered by importance, but rather grouped by the subcommittee into related categories.

- 1. *Energy efficiency:* The goal is to achieve exascale using 20 MW of power, yet existing circuits consume an order of magnitude too much power to meet this goal. Without much more energy-efficient circuits, architecture, power conversion, power delivery and cooling technologies, the total cost of ownership for exascale systems could be 10 times higher than today.

- 2. Interconnect technology: The performance of the interconnect is key to extracting the full computational capability of a computing system. Without a high performance, energy-efficient interconnect, an exascale system would be more like the millions of individual computers in a data center, rather than a supercomputer.

- 3. *Memory technology:* Many new memory technologies are emerging, including stacked memory, non-volatile memory, and processor-in-memory. All of these need to be evaluated for use in an exascale system. Minimizing data movement to this memory and making it more energy efficient are critical to developing a viable exascale system. Science requirements for the amount of memory will be a significant driver of overall system cost.

- 4. Scalable system software: Present system software was not designed to handle the exponentially growing scale of leadership-class systems. Overall management of the power and resilience of the millions of nodes in an exascale system will be the responsibility of the system software.

- 5. *Programming systems:* The present CSP model doesn't include resilience and puts all the burden of locality and parallelization on the application developers. Exascale systems will have billion-way parallelism, and frequent faults. More expressive programming models are needed that can deal with this behavior and simplify the developer's efforts.

- 6. *Data management:* There is an explosion in both the amount and complexity of the data being generated by experiments and simulations. Without significant improvements in data management, the answers in the data will never be found.

- 7. *Exascale algorithms:* There are many thousands of man-years invested in the scientific and engineering codes now in use. Changing them to run with billion-way parallelism will require redesigning, or even reinventing, the algorithms used in them, and potentially reformulating the science problems. Understanding how to do these things efficiently and effectively will be key to solving mission-critical science problems at exascale.

- 8. Algorithms for discovery, design, and decision: It is anticipated that the need for methods and software to efficiently carry out uncertainty quantification and optimization on complex multi-physics problems will be a key need at exascale.

- 9. Resilience and correctness: Getting the correct answer on exascale systems with frequent faults, lack of reproducibility in collective communication, and new mathematical algorithms with limited verification will be a critical area of investment. Getting the wrong answer really fast is of little value to the scientist.

- 10. Scientific productivity: Programming tools, compilers, debuggers, and performance enhancement tools will all play a big part in how productive a scientist is when working with an exascale system. Without increasing programming productivity, an application may run in a few hours or days at exascale, but it may take months for the scientist to get it ready to run.

#### 2.2 Integrating the Results

For the last two decades, the HPC community has successfully used a strategy based on the largescale integration of commercial-off-the-shelf (COTS) microprocessors into massively parallel supercomputing systems. In recent years, issues with the level of performance realized at scale have led to questions about the continued viability of this strategy, and the need for research to address this problem. Addressing the top ten exscale research challenges should alleviate many of these concerns, but it is not enough.

All exascale research activity will need to be organized, coordinated, and funded in the context of, and in support of, an integrated system design that is focused on meeting the performance, productivity, and energy requirements associated with the anticipated mission-driven exascale workflows of the institutions that will ultimately acquire these systems. The general principle must be that one can't design in isolation. A collection of separate, disjointed research activities, each aimed at optimizing a single design aspect or technology, will likely result in a suboptimal overall solution. The realization of an exascale system will involve a complex, multidimensional tradeoff between hardware (processors, memory, energy efficiency, reliability, interconnectivity), software (programming models, scalability, data management, productivity) and algorithms. Thus, a total systems approach is necessary, implying co-design of hardware and software, and such a total systems approach must inform the research programs for exascale [33, 34, 114].

Advancing to exascale will require innovations in architecture to integrate the many research results from diverse fields including silicon, memory, packaging, system software, interconnect, signaling and optical technologies, mathematics, and programming models. Exascale architecture requires finding the right balance of these technologies to achieve density, cost, performance and power efficiency at the appropriate levels. Research in exascale architecture will leverage the learning and experience gained in developing and using intermediate systems, and will result in improvements to some of the key elements of architecture, programming models, and system software. Exascale system design will be an optimization problem involving a set of constraints, a set of metrics for evaluating those constraints, and a methodology for evaluating them.

#### 2.3 Overview

This report is focused on identifying and explaining the top ten research challenges that must be overcome to create an effective exascale computing system. The next ten sections of the report each address one of the challenges. They include why the challenge is thought to be in the top ten, credible technical approaches for overcoming them, and the impact these results will have on the overall exascale system. The structure of the sections varies a bit, reflecting the personal styles of the experts who contributed them. While progress on the top ten research challenges may initially proceed independently, an effective exascale system will require balance and integration of the results. Issues related to a execution models, architecture, co-design methodology, modeling, and system integration are discussed in section 13.

Finally, in the course of conducting this study, the subcommittee considered a number of related issues that add context to the top ten research challenges and the means to overcome them. To further assist the DOE in planning its future research directions, this report elaborates on these additional findings and makes recommendations that, in the aggregate, contribute to advancing U.S. capacity to develop and apply exascale computing.

#### 3 Energy Efficiency

The Tianhe-2 system in China, which is number one in the current TOP500 list, consumes 17.8 megawatts (MW) to deliver 33.86 PFlops  $(10^{15} \text{ floating point operations per second)}$  on the HPL benchmark [117]. The current top supercomputers typically have an energy efficiency of 2–4 GFlops/W [51]. Thus, an exascale computing system (~  $10^{18}$  Flops) with a power budget of 20 MW will need at least an order-of-magnitude improvement in energy efficiency as compared to today's systems. To address this challenge, the energy efficiency of basic compute blocks, interconnections between the blocks, and the memory subsystem all need to be considered. Successful energy management at exascale will require research that cuts across all aspects of the design and must be integral to all design elements. Energy management will need to be practiced from the very concept of the system, and driven into base technology elements. It impacts silicon technology, circuit and chip design as well as design tools, power delivery subsystems throughout the design, system interconnect, memory and storage design, system packaging and system control software. As discussed in this section, research is needed to guide the evolution of power management from the largely static and hardware-focused environments of today to a much more dynamic process, requiring significant software support and interoperation with the underlying hardware.

#### 3.1 Aggressive versus Revolutionary Technologies

An exascale program will accelerate the introduction of advanced technology for research and for commercial use. Given the challenges in energy efficiency, aggressive use of existing (or evolutionary) low power technologies and design techniques will be required. However, some revolutionary approaches are likely to be necessary as well.

A balanced approach is required between such "aggressive evolutionary" and any "revolutionary" technologies. Exotic technologies typically have the following properties:

- They almost always cost more and take longer to go from laboratory demonstrations to system readiness than initially predicted;

- They require significant application and system software restructuring efforts and costs;

- They require significant efforts in new design tools, qualification processes, test methodology and equipment, etc.;

- They take much longer to be commercially viable (vs building a single system) and hence can be economically unviable.

A balanced approach will apply radically new technologies only where necessary, and with strict management of the above risks. The long term exploration of such technologies should be encouraged as part of advanced research programs, independent of important product or mission critical systems development. When, at a future decision checkpoint, some revolutionary technologies look viable for exascale application, further investment would be required in hardware and software tools, qualification, bring-up and test issues in preparation for the introduction of these technologies. When organized this way, an exascale program should be flexible enough to introduce radically new technologies, should they mature early.

As evolutionary device/chip technologies we can count, for example, the aggressive use of clock gating, power gating, and dynamically adaptive voltage/frequency domains. Three-dimensional (3D) stacking is promising for integrated power regulation and distribution, and is promising for

memory density, energy efficiency, and processing-in-memory. The high device density may lead to power delivery and cooling challenges. For applications that do not critically require the integration advantages, 3D integration will initially be more costly than the same functionality on separate components, and large-scale commercial viability is a concern.

CMOS and related field effect technologies (FETs) are fundamentally limited by the "Boltzmann tail" of electrons tunneling through sub-threshold voltage barriers, which gives rise to sub-threshold leakage power. The room temperature sub-threshold slope of 60 mV/decade of current FETs implies that reliable CMOS operation, with high performance (i.e. high on-to-off current ratio), requires operation at voltages above 0.55-0.6V. Low-temperature operation increases the sub-threshold slope and enables lower voltage operation, but is costly to achieve, may not lead to overall energy savings at the systems level, and does not have a commercially viable outlook. Very low (near threshold) voltage operation is another such aggressive/evolutionary technology, that can be applied to current CMOS technologies, and is the subject of the next subsection.

In contrast, revolutionary technologies are centered on exploratory devices. Some (e.g., carbon nanotubes) are still subject to Boltzmann tail behavior and will help perhaps a generation of device scaling, and may help with further voltage scaling to perhaps 0.3V. Other emerging "steep slope" (non-Boltzmann) device technologies hold promise for true low voltage operation, (e.g., tunnel FETs, piezo FETs, and spin based devices). Different device characteristics may lead to a hybrid approach, e.g. fast C-tube/tunnel/piezo FETs for logic and slow spin-based devices for arrays. These new device technologies will face issues such as materials, device scalability, performance, and reliability. Research on these post-CMOS devices is organized under the auspices of the Nanoelectronics Research Initiative of the Semiconductor Research Corporation (NRI/SRC).

Moderate funding would be required to accelerate research and reach a decision checkpoint for a few of the most promising exploratory device candidates. This would fund device research, circuit/chip design tools to create test chips of appreciable complexity, and test chips. Then the market (i.e., mobile, internet-of-things, power harvesting applications) will take over commercial development. An exascale program should be ready to leverage such a development and provide funding to accelerate design tools and system design.

#### 3.2 Near Threshold Voltage (NTV)

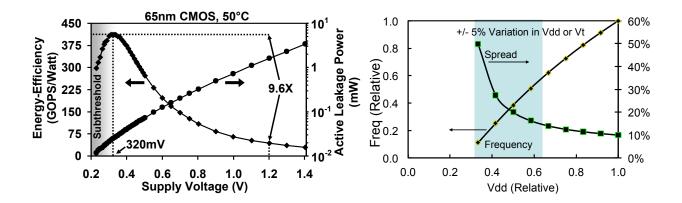

The concept of operating near the threshold voltage (NTV) of a transistor is well established, and can provide up to a 10-fold increase in energy efficiency especially for the basic compute blocks. However, it poses numerous implementation challenges needing maturity, rethinking of system architecture, and design technologies to successfully adopt it into future systems. Figure 1 shows experimental results of NTV operation and energy efficiency in 65 nm technology, which were subsequently confirmed on 45, 32, and 22 nm technologies [2, 63, 67, 68]. As the supply voltage is reduced, energy efficiency increases by an order of magnitude. However, it also poses the following system challenges:

- 1. Variability in the speed of operation of individual circuit blocks increases dramatically to almost 50%,

- 2. As the frequency of operation is lowered, logic throughput is reduced, which increases the demand for concurrency

- 3. Stability of small signal circuits such as SRAM reduces significantly, and

- 4. Sub-threshold leakage power becomes a substantial portion of the total power.

Figure 1: Energy efficiency and variability in NTV operation.

The increased variability in circuit speed poses both a circuit design and a system challenge. The gate-to-gate variability calls for the development of appropriate circuit design techniques and corresponding design tools. From a system perspective, variability in core-to-core or thread-to-thread speed will impact synchronization (barriers) in multi-threaded/multi-core processors, with further possible impact on system software.

Reduction in the logic throughput is addressed by increased parallelism, replicating logic blocks (cores) to maintain the throughput. However, this will compound an issue already encountered in the current petascale era, with about a million processor cores per system. At current core performance, the number of processor cores for exascale machines will grow to the order of a billion. However, if the number of cores will have to be increased additionally also to restore the logic throughput for a given workload running at very low frequency, then the software may need to deal with another order-of-magnitude growth in the number of cores. This approach carries the implied assumption that that any given exascale workload can be distributed over more cores without adverse effects. This assumption is valid for only a few HPC workloads today (and even in those cases, with limits to the scaling that can be achieved), and will severely limit applicability of this idea for general HPC workloads.

Stability of SRAM arrays can be addressed by: (1) replacing traditional 6T designs by 8T or 10T SRAM designs, or (2) not employing NTV to the SRAM arrays. The disproportionate subthreshold leakage power issue is addressed by employing fine grain power and energy management using power gating, and integrated power delivery subsystems, providing fine grain spatial (functional block level) and temporal (10s of nanosecond) control. All of these techniques will need careful optimization at the system level, especially with hardware/software co-design principles, to ensure that the system software can indeed exercise control, and dynamically establish the optimum operating point.

#### 3.3 Energy Efficient Architecture

Much of the "energy efficiency gap" that needs to be bridged to reach exascale goals can be achieved via more efficient architecture. Performing a double-precision floating point operation on a 28nm CMOS chip requires about 12pJ (25pJ for a double-precision fused multiply accumulate operation). A 32-bit integer operation requires only 3pJ. Yet executing one floating point instruction requires around 200pJ on a very simple, single-issue, in-order core, and upwards of 1nJ on a high-

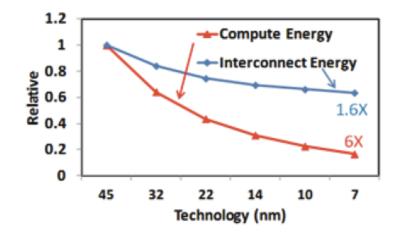

Figure 2: Compute and interconnect energy.

performance, multiple-issue, out-of-order core. Efficiency can be gained first by simplifying the core, eliminating complex logic that performs run-time, hardware scheduling, branch prediction, and other such functions that improve single-thread performance but do not affect throughput. Such simplification results in a simple, in-order core with no speculation.

Further gains are possible by reducing the overhead of instruction supply and data supply. Simply reading a 32-bit instruction from a typical 32KB instruction cache requires 20pJ - roughly the same energy as that needed to perform a 64-bit floating-point operation. Similar overheads are required by conventional data-supply mechanisms. New, streamlined instruction- and data-supply mechanisms hold the potential to dramatically improve the efficiency of even simple, in-order cores. Another promising approach is the use of compound operations, having a single instruction direct the execution of several arithmetic operations with intermediate results passed over dedicated wiring amortizes the instruction-supply overhead over many operations and eliminates the operand-supply overhead for the intermediate results.

#### **3.4 Energy Efficient Interconnects**

As semiconductor process technology scales from 22 nm today towards 7 nm and beyond, one can expect the compute (and local interconnect) energy to scale down, but as shown in Figure 2, the energy associated with longer "on-die" interconnects across-chip will not scale as much. This is because the size of the chip will remain constant across the generations, and the energy to move data across the chip will not scale much. An NTV approach will reduce the energy of computation and across-chip interconnects equally, but the energy disparity will continue to increase. We will need to adopt advanced interconnect techniques for on-die interconnects, such as low-swing differential signaling, twisted for noise immunity, and mature these technologies.

NTV, as described above, reduces compute energy, but requires more parallelism for a given throughput, demanding even more energy for data movement across the logic and the cores. Therefore, a critical balance of data movement and the extent of NTV will need to be established.

#### 3.5 Memory and Register Files

Memory and register file arrays will likely use NTV modestly, and therefore their performance will not drop as much as that of logic. As a result, to balance the performance of the compute and

Figure 3: Integrated voltage regulator.

the memory, arrays will become disproportionately larger. On the one hand this is good for data locality, reducing the need for data movement and saving energy, but on the other hand, larger arrays will consume disproportionately larger energy. Almost half of the power consumed in the arrays is due to sub-threshold leakage and therefore application of leakage management techniques will be important. This paradigm shift needs to be considered in devising the architecture of the extreme scale system to exploit larger arrays, and also employ fine grain leakage power management techniques.

#### 3.6 Efficient On-Chip Power Delivery and Management

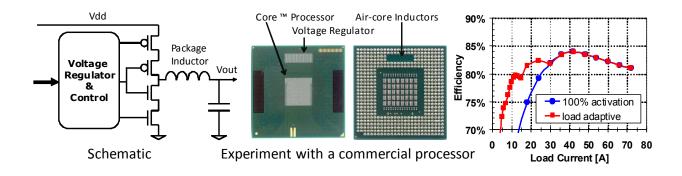

Electrically distant power delivery solutions, such as voltage regulators on boards, are not effective in fine grain power management because (1) response time is large, due to inductive effects, (2) regulators are limited in number, and (3) efficiency is not constant across a broad range of loads. Figure 3 shows an experimental integrated voltage regulator which can be implemented on the processor die itself to create multiple supply voltage rails needed for NTV operation [111]. Several regulators can be ganged together, and even distributed across the die, to improve overall efficiency across broad range of loads to allow fine grain power and energy management by bringing power delivery closer to the load.

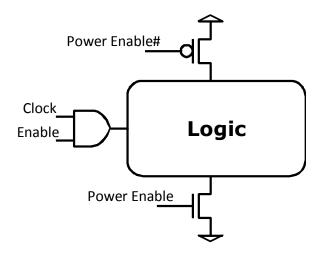

Local fine grain power and energy management can be accomplished by the well-known clockgating techniques for active power reduction, and power gating techniques for leakage power management, as shown in Figure 4. Although these techniques are well known, the challenge lies in implementation at a fine grain level, as well as state preservation when power gating is used.

An effective exascale power distribution scheme will likely include integrated voltage regulators distributed across the die with a small number of power rails. The power gates of individual cores and logic blocks can be powered up using any of these rails to dynamically select the optimal voltage and frequency controlled by the system software. Of course, at a system level, a balance will need to be struck between the increased overhead for dynamic on-chip power regulation (both in terms of control circuitry and in terms of the higher voltage that will need to be applied) and its benefit in terms of reduction of leakage power, especially for temporarily inactive circuitry.

In implementing these on-module regulators, care must be taken to both remove the heat from these devices in such a way as to not raise the temperature of the processor itself (and thus limit its performance), and to find efficient means to provide the input power to these converters. Good progress is being made in both of these directions, but more research is needed, particularly into the efficiency of the local regulators.

Figure 4: Clock and power gating.

#### 3.7 System-Scale Power Management

**Power Distribution** Typical servers today deliver power from wall plug to processor chip pins at efficiencies of about 70%. With appropriate research an exascale machine could target 90% efficiency on this path. Areas to investigate include:

- Integrated, highly reliable single stage converters

- On-chip power conversion technology

- Monolithic micro-buck converters

- Low-resistance, high-current connectors

- Lower resistance packages.

Although 20 MW is a very low total power target for an exascale system, to efficiently move this power to the computer racks the datacenter will want to target at least 480 V AC or high voltage (400 V) DC distribution. For safety reasons this voltage should be transformed down to 48 V DC for distribution in the rack, which is high enough to keep distribution losses low but low enough to be safe for handling. Continued research on efficient AC rectification and DC isolation, as well as exploitation of wide band-gap semiconductor technology, could make this stage upwards of 98% efficient. Then DC-DC conversion from the 48 V to whatever voltage is required for the on-module or on-chip power converters, plus any residual electronics being powered directly, should be made with a single stage, highly reliable converter with at least 95% efficiency. Wide band-gap semiconductor technology, coupled with better magnetic materials for the transformers and lower resistance power connectors, will allow even higher efficiencies. These new power semiconductors will require precisely tailored gate control and new very low-inductance, low-resistance packages, requiring research in these areas. The switching speed should be considered in concert with the on-module converters, so that the system can react as efficiently as possible, and allow processors to be powered at the lowest possible voltage. In general higher-frequency, faster-response converters are desirable (as they can react faster to transient loads and reduce the storage requirements of downstream converters and local capacitors). This, in turn, will drive the need for research into lower-inductance power connectors which will allow the converters to be placed inductively and resistively closer to the load. Finally the development of very compact and efficient monolithic buck-converters will allow the current trend of very specialized voltages for system-on-chip design to continue. All power converters should be made as reliable as possible, with the target of avoiding the use of redundant power supplies, which ultimately cost efficiency both through the use of ORing FETs for fault isolation and by causing the converter to operate in the less efficient low-current part of its range.

**Cooling** Almost certainly exascale systems will be water cooled to minimize floor space and reduce the cost (and energy) of cooling. A fault tolerant exascale system means nodes can be replaced while the machine runs. Hence, each node must be independently pluggable.

Designs would profit from research in

- Ultra-low thermal resistance separable thermal connections

- Improved thermal interface materials

- Very low cost, highly reliable quick-connect

- Flexible, fire-safe, highly durable polymer hoses

- Micro-channel cooling and other means for heat extraction at the component level.

Ultimately the cooling reservoir for the 20 MW Exascale system is the atmosphere. The thermal challenge can be thought of as the most energy efficient means to move the heat from the electrical and optical components of the system to this final atmospheric heat sink with minimal thermal loss along the way. Ambient water, in thermal equilibrium with the atmosphere but chemically non-corrosive, biologically inert, and without particulates that could clog small cooling orifices, is a excellent cooling fluid. However, connectors are needed to allow service of the hardware. Direct water cooling technologies (cold heads, micro-channel coolers, spray coolers and the like) will need quick-connects that allow the water hose to be disconnected and reconnected as connect circuit cards are today - at low cost, blind mate, low resistance, etc. Such quick-connects do not exist today and they impact all water cooled designs in a dramatic way. When using lower cost, but less thermally efficient indirect cooling means, such as vapor chambers, heat-pipes, thermal spreaders and the like, highly thermally conductive dry thermal interfaces are needed. Such technologies have been used for years in military applications but are still very expensive and too thermally insulating for broad use.

Finally local and national fire codes require use of fire-safe materials within the rack, even when carrying cooling fluids. Today this results in either the use of very thick, unwieldy hoses which detract from dense packaging, or very expensive formed and brazed tubing. Chemical research in polymer hoses can overcome these limitations and clear the way to very efficient water cooling direct to the thermal loads.

**Packaging** Large scale HPC systems benefit most from compact node designs indicating the need for research in:

- 3D technology

- Optical connectors

Three-dimensional chip structures can be used to dramatically lower power by allowing many more and electrically shorter connections between chips, but they carry with this even higher local power densities that drive power delivery and cooling concerns, as well as increased fragility owing to wafer thinning to expose chemically etched through-silicon vias (TSVs). Packaging research aimed at overcoming these new problems will be well received. As these 3D structures are grouped into highly energy efficient, but still higher energy, enclosures, users must retain the ability to easily service them, preferably while the rest of the equipment is still running. A the shift from 12 V to 48 V DC power will reduce distribution loss, but research which allows this higher voltage to be safely accessed may be required.

Most importantly, the pervasive use of optics in the exascale machine will require several types of optical connectors. It is entirely possible that the most difficult technical challenge to the widespread use of optical technology is the development of the required connectors. For example, optical transceivers, whether VCSEL or silicon photonic based, once integrated into the systemon-chip processor require a very high I/O density optical connector to allow the processor to be socketed and field replaceable. Such connectors are currently unavailable. A second connector is required to allow optical connections to be made between servers. Alternatively, use of active optical cables, plugged close to the source, require currently unavailable midboard connectors. Use of high port count (48 ports or more) top-of-rack switches, or larger datacenter switches based on collections of these switch chips, will require compact and closely packed optical connectors for the passive cables that connect these components. Alternatively, new packaging approaches may be developed that allow the use of anticipated dense active optical cables plugged immediately adjacent the switch chips.

#### 3.8 Impact

Following a business-as-usual approach in system design, an exascale machine is expected to consume gigawatts of power. The circuit, memory, interconnect, and platform technologies described above, both evolutionary as well as revolutionary, are expected to bring the power consumption closer to the goal of 20 MW. With hardware/software co-design approach, these technologies have potential to provide even further energy benefits to help meet the exascale power and energy goals.

#### 4 Interconnect Technology

Perhaps the most critical barrier toward realizing exascale computing is the fundamental challenge of data movement. This is for both *vertical* data movement between processors and memory as well as *horizontal* data movement between processing nodes. With the extraordinary growth in parallelism, performance is increasingly determined by how data is communicated among the numerous compute resources, rather than the arithmetic operations performed. At exascale, these challenges are daunting, as energy consumption is increasingly dominated by the cost of data movement, and is thereby the main constraint on ultimate performance.

#### 4.1 Data Movement Energy and Bandwidth Challenges

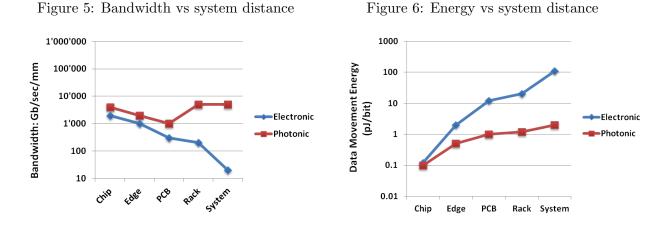

The fundamental limitations imposed by increasing energy consumption associated with moving vast data among the growing parallel compute resources has led to the so called "bandwidth taper" prevalent in current system architectures. To illustrate these interwoven bandwidth-energy challenges, Figure 5 shows the bandwidth taper (in blue) for conventional electronic interconnect technology. The units are Gbps/mm of horizontal cross-section, and bandwidth decreases by orders of magnitude as data propagates from on-chip, across the module, over the printed circuit boards, and onto the racks and the whole system. The energetic consequences of this are illustrated in Figure 6 which shows the relationship between the growing energy costs of data movement and system distance. For scaled conventional electronic interconnect technology (in blue), off-chip and inter-node communications face an order-of-magnitude energy wall associated with shrinking aggregate bandwidth and overall energy efficiency. Clearly, revolutionary data movement technology is required to create future exascale computing systems that are energy efficient and can truly scale in performance on real applications, and as Figures 5 and 6 show, photonics offers a potential solution.

The main challenge for interconnect technology has always been to provide high network bandwidth and message rates, while minimizing latency. Equally important is how effectively applications are able to utilize the network. [66] Historically, many interconnects have been built to provide these capabilities without regard to the communication mechanisms being used by the applications running on the system, leading to a bad semantic match between the communication primitives required by the applications and those provided by the network. The resulting poor utilization of the interconnect is bad for both application performance and energy efficiency.

#### 4.2 On-Die Interconnect Fabric

An on-die interconnect fabric connects cores on the die to the memory subsystem on and off the die and to the external interconnect fabric. The challenge is that the die size of the processor die will remain constant across process technology generations, and therefore the on-die interconnect energy will not scale as much (as described in section 3.4).

Investigation is needed into various on-die signaling technologies, such as repeated single-ended, differential low-swing and twisted interconnects, to determine the best interconnect technology for the processor chip. These techniques are well known, but need to be examined and methodologies developed in the context of the extreme scale processor.

Several on-die network topologies and switches have been studied, [6,58] such as a traditional bus, 2D mesh or torus with routers, crossbar switches, butterfly networks, and fat-trees, as well as circuit and packet switched networks. All of these show different characteristics, with each having benefits if used appropriately by the underlying software. The hardware choices have deep implications for the design of the communication libraries (e.g., MPI or Global Address Space), the runtime systems (scheduling and active message dispatch to the correct thread) and ultimately the applications and algorithms. The challenge is to develop network designs using these techniques that are applicable to the exascale processor, evaluate them in the context of different candidate software systems using simulations and emulations, and mature these for exascale systems.

We need to consider implementing a hierarchical network, with potentially different sub-networks at each level in the hierarchy, using the technique most suited for that level in the hierarchy, considering energy efficiency and bandwidth. For example, connecting cores in a local block is best achieved using a bus, since a bus is the most energy-efficient solution for short distances. Blocks can be connected together using a wider bus or a packet-switched network such as a mesh, or a crossbar, depending on the size and distance. It remains an open question as to whether current computing applications and algorithms can be redesigned to exploit these different potential hardware realizations. For this reason, hardware and software design must be closely coupled and not deferred until the machine arrives.

Thus, it is likely that for a processor die with O(1000) cores we will have to evolve from the conventional approach of a homogenous interconnect fabric across the chip with constant bisection bandwidth to a revolutionary approach of a hierarchical, heterogeneous, and tapered on-die interconnect fabric.

#### 4.3 Inter-chip Network Integration

The main function of the inter-chip interconnect is to provide the processors with access to remote memory. As such, the mechanisms used to integrate the network with the rest of the node architecture (processor and memory) can have a dramatic impact on how and what type of features can be effectively supported by the communication runtime. There are many available options for integrating the network. Logically, the network can be connected as an I/O device, or as a peer on the processor or memory network. Additionally, the network interface controller (NIC) can be either coherent or non-coherent with the processor cache hierarchy. Physically, the network can be integrated on-die, on-package, or on-board. Each integration choice comes with a set of tradeoffs.

As CMOS process technology continues to advance, it has already become feasible to integrate portions of the network on the same die or package as the processor. This tighter integration can provide significant energy savings, as well as opportunities for significantly enhanced functionality. By moving significant packet processing functions from software into the networking hardware (i.e, "processing-in-network"), this trend has also been contributing to reductions in network latency. A major challenge with integrating the network for high performance computing will be identifying the proper function to include in the NIC, as well as identifying a suitable network protocol to enable cross-vendor compatibility. Commodity computing will inevitably drive this market toward integrated networks designed to work well for the general Internet. Such networks will provide no advantage to high end scientific computing.

On the other hand, careful selection of advanced network capabilities, such as remote direct memory access (RDMA), remote atomic memory operation support, virtual memory enhancements to reduce overhead of memory registration, integration with complex memory hierarchies, advanced message completion notification, communication protocol offload, in-network processing of collective operations, and active messaging support, could enable the extreme scalability required for exascale computing. Making the best tradeoffs in enabling these capabilities will require a deep understanding of the requirements of large scale scientific computing applications.

#### 4.4 Photonics